The Circuit Semantics

The basic circuit translation

### Synchronous Languages—Lecture 07

Prof. Dr. Reinhard von Hanxleden

Christian-Albrechts Universität Kiel Department of Computer Science Real-Time Systems and Embedded Systems Group

20 Nov. 2018

Last compiled: November 18, 2018, 16:52 hrs

Esterel V—The Constructive Circuit Semantics

CAU

**Synchronous Languages**

Lecture 07

Slide 1

**Synchronous Languages**

Lecture 07

Slide 3

### The 5-Minute Review Session

- 1. What is the derivative (Ableitung) of a program?

- 2. How is the program transition of an Esterel program defined?

- 3. How do program transitions express logical coherence?

- 4. Which semantics for Esterel exist?

- 5. What are the constructive coherence laws, how do they differ from the logical coherence law?

CAU

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

Overview

The Circuit Semantics

Constructive circuits The basic circuit translation

### Translating Esterel to Circuits

- ► Can consider Esterel programs as SW or HW descriptions

- ▶ As it turns out, the HW-equivalent of constructiveness is that the synthesized circuit is delay-independent

- ► This gives a firm, physical base for the constructive semantics we just considered

- ► Can in turn simulate this synthesized HW-circuit in SW

- ► This is just what the Esterel v5 compiler does

- Can then also take advantage of HW optimization techniques

- ▶ Use BDD-based techniques to check constructiveness

CAU Slide 2 CAU Slide 4 **Synchronous Languages** Lecture 07 Lecture 07 Synchronous Languages

Constructive circuits

The basic circuit translation Translating the Esterel kernel The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

#### Circuit Semantics—Introduction

```

module P1:

input I;

output 0;

signal S1, S2 in

present I then emit S1 end

||

present S1 else emit S2 end

||

present S2 then emit 0 end

end signal

end module

```

```

\equiv \begin{array}{|c|c|c|}\hline \text{circuit C1:} \\ \text{S1} = \text{I} \\ \text{S2} = \neg \text{S1} \\ \text{O} = \text{S2} \\ \end{array}

```

- ► Resulting circuit is acyclic

- ► Hence always stabilizes

- ► Reactive and deterministic

CAU

Synchronous Languages

Lecture 07

Slide 5

The Circuit Semantics

Constructive circuits

Translating the Esterel kern

#### Circuit Semantics—Introduction

```

module P3:

output 0;

present 0 else emit 0 end

end module

circuit C3:

O = ¬O

```

- ► Resulting circuit never stabilizes

- ► Not reactive

### Circuit Semantics—Introduction

```

module P4:

output 0;

present 0 then emit 0 end

end module

circuit C4:

O = O

```

- ▶ Resulting circuit can stabilize at different values

- ► Not deterministic

C | A | U Synchronous Languages Lecture 07 Slide 7

The Circuit Semantics

Constructive circuits

The basic circuit translation

#### Circuit Semantics—Introduction

```

module P9:

[

present 01 then emit 01 end

] present 01 then

present 02 else emit 02 end

end

]

```

```

\begin{array}{c|c}

\hline

\hline

01 = 01 \\

02 = 01 \land \neg 02

\end{array}

\begin{array}{c|c}

\hline

01

\end{array}

```

circuit C9:

- ► Reactive and deterministic

- But not constructive!

C | A | U Synchronous Languages Lecture 07 Slide 8

Constructive circuits

The basic circuit translation Translating the Esterel kernel

#### Circuit Semantics—Introduction

- ► Reactive and deterministic

- ► Meaning: If it stabilizes, there is only one possible value for each wire's voltage

- ▶ But: Does it always stabilize?

C | A | U Synchronous Languages Lecture 07 Slide 9

The Circuit Semantics

#### Constructive circuits

The basic circuit translation

Translating the Esterel kerne

#### Circuit Semantics—Introduction

► Consider following delay assignment:

- ► Circuit is reactive and deterministic (Newtonian model)

- ▶ But: Circuit never stabilizes (Vibration model)

- ► Hence: Electrical stabilization is not the conjunction of reactivity and determinism!

C | A | U Synchronous Languages Lecture 07 Slide 10

This circuit can be expressed as

$$x(t) = x_1(t-1) \lor x_2(t-1)$$

with

$$x_1(t) = \neg x(t-1) \text{ and } x_2(t) = x(t-3),$$

resulting in

$$x(t) = \neg x(t-2) \lor x(t-4).$$

With x(t) = 0 for t < 0 this results in an oscillation of x, with period 2.

Constructive circuits

The basic circuit translation Translating the Esterel kernel

#### Circuit Semantics—Introduction

module P13:

present I then

present 02 then emit 01 end

else

present 01 then emit 02 end

end

- ► Reactive and deterministic

- Cyclic, yet always stabilizes

- ► Hence: Electrical stabilization does not require acyclicity

- ▶ In fact: Electrical stabilization equivalent to constructiveness

C | A | U Synchronous Languages Lecture 07 Slide 11

The Circuit Semantics

Constructive circuits

The basic circuit translation Translating the Esterel kerne

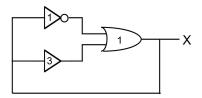

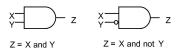

#### Constructive Circuits

Basic building blocks

Z = X or Y Z = not(X or Y)

$$X \longrightarrow Z$$

$X \longrightarrow Z$   $Z = reg(X)$

- ► Allow insertion of arbitrary delays

- ► Registers:

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

#### Constructive Circuits

#### Constructive Boolean (intuitionistic) logic:

- ► Evaluate equations with constant folding rules

- ightharpoonup not  $0 \rightarrow 1$

- ightharpoonup 1 or  $x \rightarrow 1$

- ightharpoonup x or 1 o 1

- ightharpoonup 0 or  $0 \rightarrow 0$

- ightharpoonup 0 and  $x \to 0$

- $\triangleright$  x and  $0 \rightarrow 0$

- ightharpoonup 1 and 1 o 1

- ▶ There is no law of excluded middle (x or not  $x \to 1$ )!

- ➤ Circuit equations yield solution iff circuit is delay insensitive (i.e., the original Esterel program is constructive)

- ▶ Propagation of 1's corresponds to *Must*-analysis

- Propagation of 0s corresponds to Cannot-analysis

C | A | U Synchronous Languages Lecture 07 Slide 13

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel k

#### The Basic Circuit Translation

- Structural translation

- ► Follows state semantics

- ► Associate registers with "1" statements (pause)

- ► Associate combinational logic with all other statements

- ▶ Build up program-circuit from subcircuits

- ► Additional boot register to implement initial state

- ► Basic circuit translation does not address schizophrenia (see later)

C | A | U Synchronous Languages Lecture 07 Slide 12 C | A | U Synchronous Languages Lecture 07 Slide 14

Constructive circuits

The basic circuit translation

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

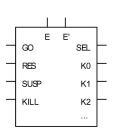

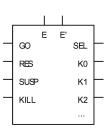

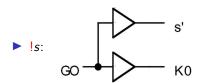

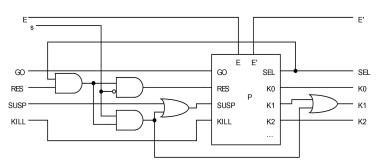

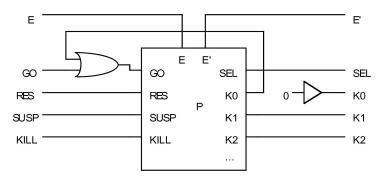

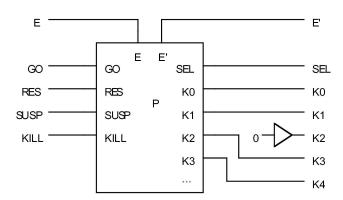

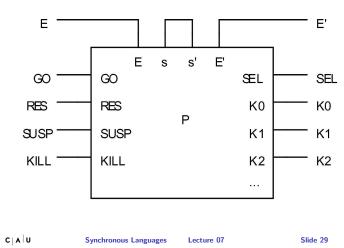

#### Interface for subcircuits

#### Inputs:

- ► GO: Starts statement afresh

- ► RES: Resumes execution of a selected statement

- ► SUSP: Suspend execution of the statement

- Registers keep their current value unless killed because of the KILL input

Slide 15

Slide 16

► KILL: Unsets statement's registers in case of a trap exit

C | A | U Synchronous Languages Lecture 07

The Circuit Semantics

Synchronous Languages

Constructive circuits

The basic circuit translation

Interface for subcircuits contd.

CAU

#### Outputs:

- ➤ SEL: Indicates that a state in statement is currently selected for resumption, i.e. that some internal pause register is set

- ls simply the disjunction of the internal registers.

- ► K0, K1, ...: Completion codes (1-hot encoding)

Lecture 07

#### Interface for subcircuits contd.

- ► E and E': input/output signal interface

- ► Are compound pins or buses

- Contain one elementary pin per signal visible in the scope of the current statement.

- May freely extract specific signals s or s' out of E or E'.

- ► As for the K pins, the E' pins are explicitly unset when the statement is not executed

- ▶ I.e. when  $\neg$ ( GO  $\lor$  ( RES  $\land$  SEL))

C | A | U Synchronous Languages Lecture 07 Slide 17

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

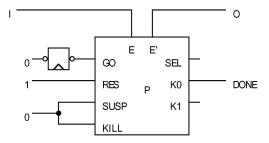

#### The Global Environment

- ▶ Boot register sets GO input in initial instant

- ► At each clock cycle

- set RES

- clock the registers

$\mathbf{C} \mid \mathbf{A} \mid \mathbf{U}$  Synchronous Languages Lecture 07 Slide 18

- Note that the initial 1 for RES does no harm, as no register is selected yet

- ▶ SEL and K1 are not needed globally

- ► The output signal are also fed back to the input signals—as if they were declared as signals at the top-level (see signal declaration later)

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

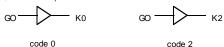

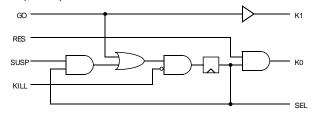

## Translating the Esterel Kernel

▶ Completion, with  $k \neq 1$ :

k = 1 (pause):

C | A | U Synchronous Languages Lecture 07 Slide 19

Use these conventions to simplify diagrams:

- ▶ Unused inputs are not pictured.

- ▶ Not all outputs are pictured. An omitted output is assumed to be explicitly unset, i.e. to be driven by a 0 constant

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

# Translating the Esterel Kernel

The Circuit Semantics

C | A | U Synchronous Languages Lecture 07 Slide 20

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

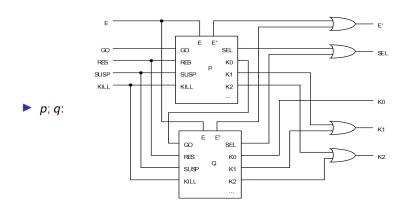

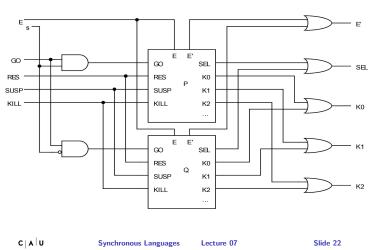

### Translating the Esterel Kernel

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

## Translating the Esterel Kernel

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

C | A | U Synchronous Languages Lecture 07 Slide 21 C | A | U Synchronous Languages Lecture 07 Slide 23

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

C | A | U Synchronous Languages Lecture 07 Slide 24

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

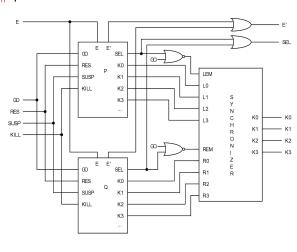

### **▶** *p* || *q*:

CAU

Synchronous Languages Lecture 07 Slide 25

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

- **▶** *p* | *q* (contd):

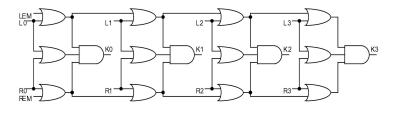

- ► The synchronizer computes the maximum of the completion codes

- ► Implemented with this (constructive) circuit:

C | A | U Synchronous Languages Lecture 07 Slide 26

► The inputs LEM and REM indicate the case where the sets of completion codes are empty—which is the case if neither GO is set nor one of the internal registers

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

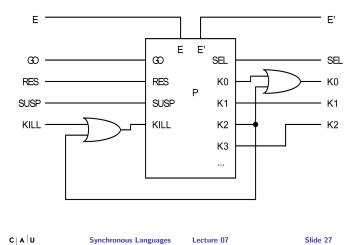

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

## Translating the Esterel Kernel

**▶** ↑*p*:

C | A | U Synchronous Languages Lecture 07 Slide 28

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Translating the Esterel Kernel

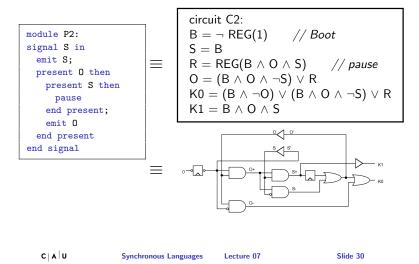

**▶** *p*\*s*:

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

The Circuit Semantics

Constructive circuits

The basic circuit translation

Translating the Esterel kernel

### Example

Can you find the bug in the diagram?

► (Hint: have a look at the O- gate)

When evaluating this, it turns out that in the initial instant, it is

- ► B = S = 1

- ightharpoonup R = 0 = 0

- ightharpoonup K0 = 1—hence this terminates after the first instance

- ightharpoonup K1 = 0—as expected, as K0 already evaluated to 1

### To Go Further

▶ Gérard Berry, The Constructive Semantics of Pure Esterel, Draft book, current version 3.0, Dec. 2002, Chapters 10 and 11,

http://www-sop.inria.fr/members/Gerard.Berry/Papers/EsterelConstructiveBook.zip

C | A | U Synchronous Languages Lecture 07 Slide 31