### Synchronous Languages—Lecture 12

Prof. Dr. Reinhard von Hanxleden

Christian-Albrechts Universität Kiel Department of Computer Science Real-Time Systems and Embedded Systems Group

12 Dec. 2016

Last compiled: December 11, 2016, 18:51 hrs

Code Generation for Sequential Constructiveness

1. What are Statecharts?

CAU

1. What are *Statecharts*? Who invented them?

- 1. What are *Statecharts*? Who invented them?

- 2. What is the difference between SyncCharts and Statecharts?

C A U Synchronous Languages Lecture 12

Slide 2

- 1. What are *Statecharts*? Who invented them?

- 2. What is the difference between SyncCharts and Statecharts?

- 3. How can we transform Esterel to SyncCharts?

- 1. What are *Statecharts*? Who invented them?

- 2. What is the difference between SyncCharts and Statecharts?

- 3. How can we transform Esterel to SyncCharts? How about the other direction?

CAL

- 1. What are *Statecharts*? Who invented them?

- 2. What is the difference between *SyncCharts* and Statecharts?

- 3. How can we transform Esterel to SyncCharts? How about the other direction?

- 4. What are SCCharts? What is their motivation?

- 1. What are *Statecharts*? Who invented them?

- 2. What is the difference between *SyncCharts* and Statecharts?

- 3. How can we transform Esterel to SyncCharts? How about the other direction?

- 4. What are SCCharts? What is their motivation?

- 5. What are Core SCCharts?

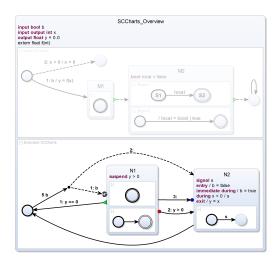

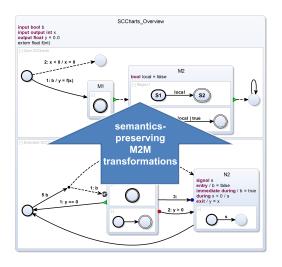

#### Overview

SCG Mapping & Dependency Analysis

Code Generation Approaches

Schizophrenia Revisited

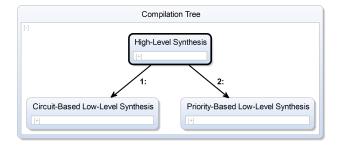

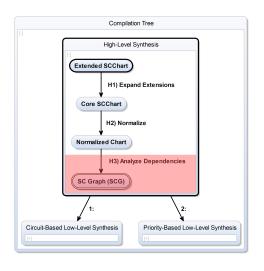

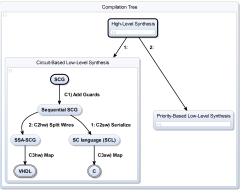

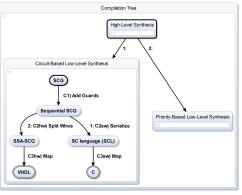

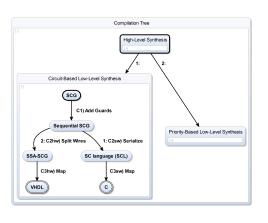

# Compilation — Overview

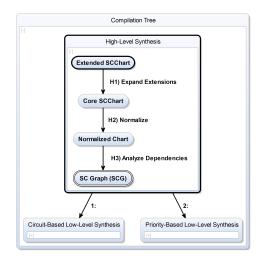

# Compilation — High-Level Synthesis

# Compilation — High-Level Synthesis

Green: covered in previous lecture

Slide 6

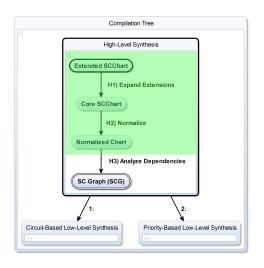

## Compilation — High-Level Synthesis

Red: coming up now

#### Overview

SCG Mapping & Dependency Analysis

Compilation Overview

The SC Graph

Dependency Analysis

Code Generation Approaches

Schizophrenia Revisited

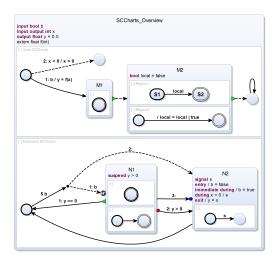

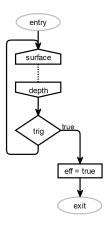

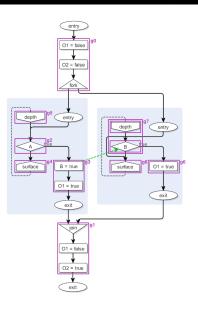

# The SC Graph

SC Graph:

Labeled graph G = (S, E)

# The SC Graph

#### SC Graph:

Labeled graph G = (S, E)

► Nodes S correspond to statements of sequential program

# The SC Graph

#### SC Graph:

Labeled graph G = (S, E)

- ► Nodes *S* correspond to statements of sequential program

- ► Edges *E* reflect sequential execution control flow

# High-Level Step 3: Map to SC Graph

|          | Region<br>(Thread) | Superstate<br>(Concurrency) | Trigger<br>(Conditional) | Effect (Assignment) | State<br>(Delay) |

|----------|--------------------|-----------------------------|--------------------------|---------------------|------------------|

| SCCharts | 0                  | [-]t1<br>[-]12              | 11:0 2:                  | 1/x = e             |                  |

Slide 10

# High-Level Step 3: Map to SC Graph

|          | Region<br>(Thread) | Superstate (Concurrency)  | Trigger<br>(Conditional)  | Effect<br>(Assignment) | State<br>(Delay) |

|----------|--------------------|---------------------------|---------------------------|------------------------|------------------|

| SCCharts | 0                  | [-]tt                     | /1: c 2:                  | 1/x = e                |                  |

| scg      | entry              | fork                      | c true                    | x = e                  | surface          |

| SCL      | t                  | fork $t_1$ par $t_2$ join | if $(c)$ $s_1$ else $s_2$ | x = e                  | pause            |

C A U Synchronous Languages Lecture 12

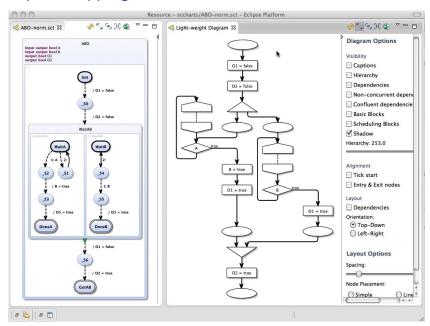

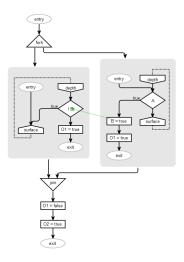

# Example: Mapping ABO to SCG

Two assignments within the SC Graph are concurrent iff

Two assignments within the SC Graph are concurrent iff

they share a least common ancestor fork node.

Two assignments within the SC Graph are concurrent iff

▶ they share a *least common* ancestor fork node.

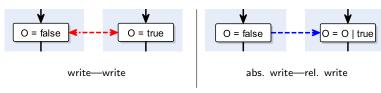

Two assignments are confluent iff

Two assignments within the SC Graph are concurrent iff

▶ they share a *least common* ancestor fork node.

Two assignments are confluent iff

the order of their assignments does not matter.

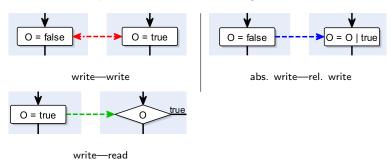

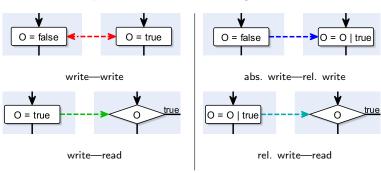

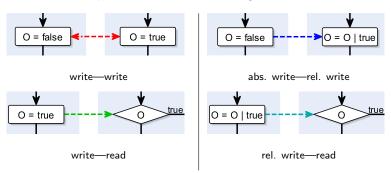

write-write

#### Dependencies are further categorized in

The SC MoC employs a strict "initialize - update - read" protocol.

(More on the SC MoC will follow in next lecture.)

### Overview

#### SCG Mapping & Dependency Analysis

#### Code Generation Approaches

Circuit-based Approach Priority-based Approach Approach Comparison

Schizophrenia Revisited

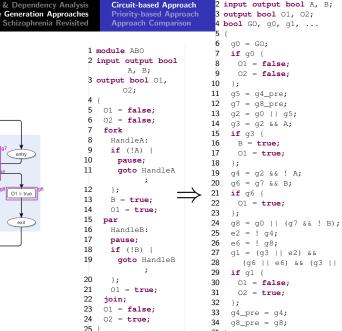

## Low-Level Synthesis I: The Circuit Approach

- Basic idea: Generate netlist

- Precondition:

Acyclic SCG

(with dependency edges, but without tick edges)

- Well-established approach for compiling SyncCharts/Esterel

### Low-Level Synthesis I: The Circuit Approach

- Basic idea: Generate netlist

- Precondition: Acyclic SCG (with dependency edges, but without tick edges)

- Well-established approach for compiling SyncCharts/Esterel

#### Differences to Esterel circuit semantics [Berry '02]

- 1. Simpler translation rules, as aborts/traps/suspensions already transformed away during high-level synthesis

- 2. SC MoC permits sequential assignments

#### Basic Block:

A collection of SCG nodes / SCL statements

that can be executed monolithically

#### Basic Block

A collection of SCG nodes / SCL statements

that can be executed monolithically

#### Rules:

Split at nodes with more than one incoming control flow edge

#### Basic Block

A collection of SCG nodes / SCL statements

that can be executed monolithically

- Split at nodes with more than one incoming control flow edge

- Split at nodes with more than one outgoing control flow edge

#### Basic Block:

A collection of SCG nodes / SCL statements

that can be executed monolithically

- Split at nodes with more than one incoming control flow edge

- Split at nodes with more than one outgoing control flow edge

- Split at tick edges

#### Basic Block

A collection of SCG nodes / SCL statements

that can be executed monolithically

- Split at nodes with more than one incoming control flow edge

- Split at nodes with more than one outgoing control flow edge

- Split at tick edges

- Split after fork nodes and before join nodes

#### Basic Block

A collection of SCG nodes / SCL statements

that can be executed monolithically

- Split at nodes with more than one incoming control flow edge

- Split at nodes with more than one outgoing control flow edge

- Split at tick edges

- Split after fork nodes and before join nodes

- Each node can only be included in one basic block at any time

Basic blocks may be interrupted when a data dependency interferes.

- Basic blocks may be interrupted when a data dependency interferes.

- Structure basic blocks further: Scheduling Blocks

- Basic blocks may be interrupted when a data dependency interferes.

- Structure basic blocks further: Scheduling Blocks

- ► Rules:

- Split a basic block at incoming dependency edge

- Basic blocks may be interrupted when a data dependency interferes.

- Structure basic blocks further: Scheduling Blocks

- Rules:

- Split a basic block at incoming dependency edge

- But...

- want to minimize the number of context switches

- ▶ ⇒ Room for optimization!

|                                | Trigger<br>(Conditional) | Effect (Assignment) | State<br>(Delay) | Region<br>(Thread) | Superstate (Concurrency) |

|--------------------------------|--------------------------|---------------------|------------------|--------------------|--------------------------|

| Normalized<br>Core<br>SCCharts | /1: c \2:                | i/x = e             |                  | 0                  | (-) t5                   |

|                                | Trigger (Conditional)   | Effect<br>(Assignment) | State<br>(Delay) | Region<br>(Thread) | Superstate (Concurrency)  |

|--------------------------------|-------------------------|------------------------|------------------|--------------------|---------------------------|

| Normalized<br>Core<br>SCCharts | /1: c \2:               | /x = e                 |                  |                    | 1912<br>[911              |

| SCL                            | if (c) $s_1$ else $s_2$ | <i>X</i> = <i>e</i>    | pause            | t                  | fork $t_1$ par $t_2$ join |

| SCG                            | ctrue                   | x = e                  | surface          | entry exit         | fork                      |

|                                | Trigger<br>(Conditional)                                                | Effect<br>(Assignment)                | State<br>(Delay)                                              | Region<br>(Thread)                                                          | Superstate (Concurrency)                                                                             |

|--------------------------------|-------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Normalized<br>Core<br>SCCharts | /1: c \2:                                                               | i/x = e                               |                                                               |                                                                             | [-] t1                                                                                               |

| SCL                            | if (c) $s_1$ else $s_2$                                                 | <i>X</i> = <i>e</i>                   | pause                                                         | t                                                                           | fork $t_1$ par $t_2$ join                                                                            |

| SCG                            | ctrue                                                                   | x = e                                 | surface                                                       | entry                                                                       | fork                                                                                                 |

| Data-Flow<br>Code              | $g = \vee g_{in}$ $g_{true} = g \wedge c$ $g_{false} = g \wedge \neg c$ | $g = \forall g_{in}$ $x' = g ? e : x$ | $g_{surf} = \vee g_{in}$<br>$g_{depth} =$<br>pre $(g_{surf})$ | $d = g_{exit}$ $m = \neg (g_{fork} \lor \lor \lor_{depth \in t} g_{depth})$ | $g_{fork} = \vee g_{in}$ $g_{join} = (d_1 \vee m_1)$ $\wedge (d_2 \vee m_2)$ $\wedge (d_1 \vee d_2)$ |

| Circuits                       | g glabe                                                                 | - r'                                  | $g_{surf}$ — $g_{depth}$                                      | 9fork<br>9depth1<br>9depth2                                                 | $m_1$ $d_1$ $d_2$ $d_2$ $d_3$ $d_4$ $d_4$                                                            |

## ABO SCG, With Dependencies and Scheduling Blocks

## ABO SCG, With Dependencies and Scheduling Blocks

```

1 module ABO

2 input output bool

A, B;

3 output bool 01,

02;

O1 = false;

02 = false;

fork

8

HandleA:

if (!A) {

10

pause;

11

goto HandleA

12

};

13

B = true:

14

01 = true;

15

par

16

HandleB:

17

pause;

18

if (!B) {

19

goto HandleB

20

};

21

01 = true:

22

join;

23

O1 = false;

24

02 = true;

25

```

entry

O1 = false

O2 = false

entry

B = true

O1 = true

exit

O1 = false

O2 = true

exit

surface

35 }

depth

surface

## Sequential SCG — ABO

## (Recall) Low-Level Synthesis I: The Circuit Approach

- Can use sequential SCL directly for SW synthesis

- Synthesizing HW needs

a little further work

```

1 module ABO-seq

2 input output bool A, B;

3 output bool 01, 02;

4 bool GO, q0, q1, ...

5

q0 = GO;

if q0 {

01 = false:

02 = false:

10

};

11

q5 = q4_pre;

12

q7 = q8_pre;

13

g2 = g0 | | g5;

14

q3 = q2 \&\& A;

15

if q3 {

16

B = true;

17

01 = true;

18

19

q4 = q2 \&\& ! A;

20

q6 = q7 && B;

21

if q6 {

22

01 = true;

23

};

24

q8 = g0 \mid \mid (g7 \&\& ! B);

25

e2 = ! q4;

26

e6 = ! q8;

```

```

1 module ABO-seq

2 input output bool A, B;

3 output bool 01, 02;

4 bool GO, q0, q1, ...

5

q0 = GO;

if q0 {

01 = false:

02 = false:

10

};

11

q5 = q4_pre;

12

q7 = q8_pre;

13

g2 = g0 | | g5;

14

q3 = q2 \&\& A;

15

if q3 {

16

B = true;

17

01 = true;

18

};

19

q4 = q2 \&\& ! A;

20

q6 = q7 && B;

21

if q6 {

22

01 = true;

23

};

24

q8 = g0 \mid \mid (g7 \&\& ! B);

25

e2 = ! q4;

26

e6 = ! q8;

```

```

1 module ABO-seq

2 input output bool A, B;

3 output bool 01, 02;

4 bool GO, q0, q1, ...

5

a0 = G0:

if a0 {

01 = false;

02 = false:

10

};

11

q5 = q4_pre;

12

q7 = q8_pre;

13

g2 = g0 | | g5;

14

g3 = g2 && A;

15

if q3 {

16

B = true;

17

01 = true:

18

};

19

q4 = q2 \&\& ! A;

20

q6 = q7 && B;

21

if q6 {

22

01 = true;

23

};

24

q8 = q0 \mid \mid (q7 \&\& ! B);

25

e2 = ! q4;

26

e6 = ! q8;

```

- Difference to software

- All persistence (state, data) in external reg's ("\_pre"-var's)

- ▶ Permit only one value per wire per tick ⇒ SSA

```

1 module ABO-seq

2 input output bool A, B;

3 output bool 01, 02;

4 bool GO, q0, q1, ...

5

a0 = G0:

if a0 {

01 = false;

02 = false:

10

};

11

q5 = q4_pre;

13 q2 = q0 \mid | q5;

14

q3 = q2 && A;

15

if q3 {

16

B = true;

17

01 = true:

18

};

19

q4 = q2 \&\& ! A;

20

q6 = q7 && B;

21

if q6 {

22

01 = true;

23

};

24 q8 = g0 || (g7 && ! B);

25 e2 = ! q4;

26

e6 = ! q8;

```

- frerence to software

- All persistence (state, data) in external reg's ("\_pre"-var's)

- Permit only one value per wire per tick ⇒ SSA

```

1 ARCHITECTURE behavior OF ABO IS

2 -- local signals definition, hidden

3 begin

4 -- main logic

5 q0 <= GO local;

6 01 <= false WHEN g0 ELSE 01_pre;

7 02 <= false WHEN q0 ELSE 02 pre;

8 q5 <= q4 pre;

9 q7 <= q8 pre;

10 q2 <= q0 or q5;

11 q3 <= q2 and A local;

12 B <= true WHEN g3 ELSE B_local;

13 01 2 <= true WHEN q3 ELSE 01;

14 q4 <= q2 and not A local;

15 q6 <= q7 and B;

16 01_3 <= true WHEN g6 ELSE 01_2;

17 g8 <= g0 or (g7 and not B);

18 e2 <= not (q4);

19 e6 <= not (g8);

```

## Low-Level Synthesis II: The Priority Approach

- More software-like

- Don't emulate control flow with guards/basic blocks, but with program counters/threads

- Priority-based thread dispatching

- ► SCL<sub>P</sub>: SCL + PriolDs

- ► Implemented as C macros

## Low-Level Synthesis II: The Priority Approach

- More software-like

- Don't emulate control flow with guards/basic blocks, but with program counters/threads

- Priority-based thread dispatching

Slide 24

- SCL<sub>P</sub>: SCL + PriolDs

- Implemented as C macros

#### Differences to Synchronous C [von Hanxleden '09]

- ▶ No preemption ⇒ don't need to keep track of thread hierarchies

- ► Fewer, more light-weight operators

- RISC instead of CISC

## Low-Level Synthesis II: The Priority Approach

- More software-like

- Don't emulate control flow with guards/basic blocks, but with program counters/threads

- Priority-based thread dispatching

- ► SCL<sub>P</sub>: SCL + PriolDs

- Implemented as C macros

#### Differences to Synchronous C [von Hanxleden '09]

- No preemption ⇒ don't need to keep track of thread hierarchies

- ► Fewer, more light-weight operators

- RISC instead of CISC

- More human-friendly syntax

### SCL<sub>P</sub> Macros I

```

1 // Declare Boolean type

2 typedef int bool;

3 #define false 0

4 #define true 1

6 // Generate " L<line-number>" label

7 #define concat helper(a, b) a ## b

8 #define _concat(a, b) _concat_helper(a, b)

9 #define label concat(L, LINE)

10

11 // Enable/disable threads with prioID p

12 #define u2b(u)

(1 << u)

13 #define enable(p) enabled |= u2b(p); active |= u2b(p)

14 #define _isEnabled(p) ((_enabled & _u2b(p)) != 0)

15 #define disable(p) enabled &= ~ u2b(p)

```

### SCL<sub>P</sub> Macros II

```

17 // Set current thread continuation

18 #define _setPC(p, label) _pc[p] = &&label

19

20 // Pause, resume at <label> or at pause

21 #define pause(label) setPC(cid, label); goto L PAUSE

22 #define pause pause (label): label:

23

24 // Fork/join sibling thread with prioID p

25 #define fork1(label, p) setPC(p, label); enable(p);

26 #define join1(p) _label_: if (_isEnabled(p)) { _pause(_label_); }

27

28 // Terminate thread at "par"

29 #define par goto L TERM;

30

31 // Context switch (change prioID)

32 #define _prio(p) _deactivate(_cid); _disable(_cid); _cid = p; \

```

### ABO SCL<sub>P</sub> I

```

85 int tick()

86 {

87 tickstart(2);

88 01 = false:

89 02 = false;

90

fork1 (HandleB,

91

1) {

HandleA:

92

93

if (!A) {

94

pause;

goto HandleA

95

;

96

B = true;

97

01 = true;

98

99

100

} par {

```

```

85 int tick()

86 {

87 if (_notInitial) { _active = _enabled;

goto L DISPATCH; } else { pc[0]

= &&_L_TICKEND; _enabled = (1 <<

0); active = enabled; cid = 2;

; _enabled |= (1 << _cid); _active

|= (1 << cid); notInitial = 1;

} ;

88 01 = 0;

02 = 0;

90

91

_pc[1] = &&HandleB; _enabled |= (1 <<

1); active |= (1 << 1); {

HandleA:

92

93

if (!A) {

pc[cid] = && L94; goto L PAUSE;

94

L94:;

goto HandleA;

95

96

B = 1:

97

01 = 1;

98

99

} goto _L_TERM; {

100

```

### ABO SCLP II

```

102

HandleB:

103

pause;

if (!B) {

104

goto HandleB

105

106

107

01 = true;

108

} join1(2);

109

O1 = false;

110

111

02 = true;

112 tickreturn;

113 }

```

```

102

HandleB:

_pc[_cid] = &&_L103; goto _L_PAUSE;

103

L103:;

if (!B) {

104

105

goto HandleB:

106

107 	 01 = 1;

108 } L108: if ((( enabled & (1 << 2)) !=

0)) { pc[cid] = && L108; goto

L PAUSE; };

109

01 = 0;

110

111 02 = 1;

112

goto L TERM; L TICKEND: return (

enabled != (1 << 0)); L TERM:

enabled &= ~(1 << cid); L PAUSE

: _active &= ~(1 << _cid);

L DISPATCH: asm volatile ("bsrl

%1,%0\n" : "=r" ( cid) : "r" (

_active) ); goto *_pc[_cid];

113 }

```

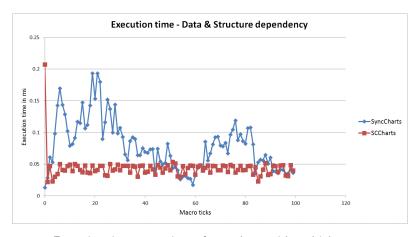

## Comparison of Low-Level Synthesis Approaches

Circuit Priority

## Comparison of Low-Level Synthesis Approaches

|                             | Circuit | Priority |

|-----------------------------|---------|----------|

| Accepts instantaneous loops | _       | +        |

| Can synthesize hardware     | +       | _        |

| Can synthesize software     | +       | +        |

## Comparison of Low-Level Synthesis Approaches

|                                              | Circuit | Priority |

|----------------------------------------------|---------|----------|

| Accepts instantaneous loops                  | _       | +        |

| Can synthesize hardware                      | +       | _        |

| Can synthesize software                      | +       | +        |

| Size scales well (linear in size of SCChart) | +       | +        |

CALU

# Comparison of Low-Level Synthesis Approaches

|                                                 | Circuit | Priority |

|-------------------------------------------------|---------|----------|

| Accepts instantaneous loops                     | _       | +        |

| Can synthesize hardware                         | +       | _        |

| Can synthesize software                         | +       | +        |

| Size scales well (linear in size of SCChart)    | +       | +        |

| Speed scales well (execute only "active" parts) | _       | +        |

| Instruction-cache friendly (good locality)      | +       | _        |

| Pipeline friendly (little/no branching)         | +       | -        |

| WCRT predictable (simple control flow)          | +       | +/-      |

| Low execution time jitter (simple/fixed flow)   | +       | _        |

CALU

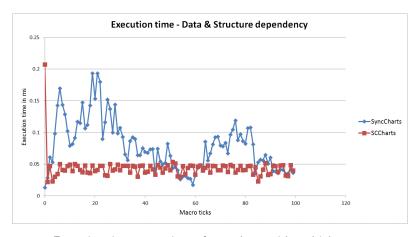

# Comparison — Jitter

Execution time comparison of statecharts with multiple hierarchies depicts

# Comparison — Jitter

Execution time comparison of statecharts with multiple hierarchies depicts

low jitter in circuit-based approach

# Comparison — Jitter

Execution time comparison of statecharts with multiple hierarchies depicts

- low jitter in circuit-based approach

- execution time in priority-based approach more dependant to structure and input data of the statechart

#### Overview

SCG Mapping & Dependency Analysis

Code Generation Approaches

#### Schizophrenia Revisited Classic Approaches

The SCL Solution

```

1 module schizo

2 output 0;

3

4 100p

signal S in

present S

then

emit 0

end:

10

pause;

11

emit S:

12

end:

13 end loop

14 end module

```

Esterel [Tardieu & de Simone '04]

```

1 module schizo-conc

2 output bool 0;

3 {

1 module schizo

while (true) {

2 output 0;

bool S, _Term;

3

4 100p

fork

signal S in

Term = false:

present S

0 = S:

then

10

pause:

emit 0

11

S = S || true;

end:

12

Term = true:

10

pause;

13

par

11

emit S:

14

while (true) {

12

end:

15

S = false;

13 end loop

16

if ( Term)

14 end module

17

break;

18

pause;

Esterel

19

20

join;

[Tardieu & de Si-

21

mone '04]

22

```

SCL (1st try)

```

1 module schizo-conc

2 output bool 0:

3

1 module schizo

while (true) {

2 output 0;

bool S, Term;

3

4 100p

fork

signal S in

Term = false;

S = S | true

present S

0 = S;

S = false

then

pause;

Term = false

Term = true

emit 0

11

S = S || true;

end:

12

_Term = true;

10

pause;

O = S

13

par

11

emit S;

14

while (true) {

12

end;

15

S = false;

13 end loop

16

if ( Term)

14 end module

17

break;

18

pause;

Esterel

19

20

[Tardieu & de Si-

ioin:

21

mone '04]

22

SCL (1st try)

```

```

1 module schizo-conc

2 output bool 0:

3

1 module schizo

while (true) {

2 output 0;

bool S, Term;

3

4 100p

fork

signal S in

Term = false;

S = S | true

present S

0 = S;

S = false

then

pause;

Term = false

Term = true

emit 0

11

S = S || true;

end:

12

_Term = true;

10

pause;

O = S

13

par

11

emit S;

14

while (true) {

12

end;

S = false;

15

13 end loop

16

if ( Term)

14 end module

17

break;

18

pause;

Esterel

19

20

ioin:

[Tardieu & de Si-

21

Q: The problem?

mone '04]

22

SCL (1st try)

```

```

1 module schizo-conc

2 output bool 0:

3

1 module schizo

while (true) {

2 output 0;

bool S, Term;

3

4 100p

fork

signal S in

Term = false;

S = S | true

present S

0 = S;

S = false

then

pause;

Term = false

Term = true

emit 0

11

S = S || true;

end:

12

_Term = true;

10

pause;

0 = S

13

par

11

emit S;

14

while (true) {

12

end;

S = false;

15

13 end loop

16

if ( Term)

14 end module

17

break;

18

pause;

Esterel

19

20

ioin:

[Tardieu & de Si-

21

Q: The problem?

mone '04]

22

A: Instantaneous loop!

SCL (1st try)

```

Term = false

0 = S

# ... What About That Acyclicity?

```

1 module schizo-conc

2 output bool 0:

3

1 module schizo

while (true) {

2 output 0;

bool S, Term;

3

4 100p

fork

signal S in

Term = false;

present S

0 = S;

then

pause;

emit 0

11

S = S || true;

end:

Term = true;

10

pause;

13

par

11

emit S;

14

while (true) {

12

end;

S = false;

15

13 end loop

16

if ( Term)

14 end module

17

break;

18

pause;

Esterel

19

20

ioin:

[Tardieu & de Si-

21

mone '04]

22

SCL (1st try)

```

Q: The problem?

A: Instantaneous loop!

a.k.a. Signal reincarnation

a.k.a. Schizophrenia

S = S | true

Term = true

S = false

#### A Solution

```

1 module schizo

2 output 0;

4 loop

signal S in

present S

then

8

emit O

9

end;

10

pause;

11

emit S;

12

end;

13 end loop

14 end module

```

Esterel

#### A Solution

```

1 module schizo-cured

2 output 0;

1 module schizo

2 output 0;

4 loop

signal S in

4 100p

present S then

signal S in

emit 0

Duplicated loop body to

present S

end:

separate signal instances

then

pause;

8

emit 0

10

emit S:

Q: Complexity?

9

end;

11

end:

10

pause;

12

signal S' in

11

emit S;

13

present S' then

12

end;

14

emit 0

13 end loop

15

end:

14 end module

16

pause;

17

emit S';

Esterel

end;

19 end loop

```

#### A Solution

```

1 module schizo-cured

2 output 0;

1 module schizo

3

2 output 0;

4 loop

signal S in

4 loop

present S then

signal S in

emit 0

Duplicated loop body to

present S

end:

separate signal instances

then

pause;

8

emit 0

10

emit S:

Q: Complexity?

9

end;

11

end:

10

pause;

12

signal S' in

11

A: Exponential ©

emit S;

13

present S' then

12

end;

14

emit 0

13 end loop

15

end:

14 end module

16

pause;

17

emit S';

Esterel

end;

19 end loop

```

```

1 module schizo

2 output 0;

3

4 100p

signal S in

present S

then

emit 0

end;

10

pause;

11

emit S;

12

end;

13 end loop

14 end module

```

#### Esterel

```

1 module

2 schizo-cured2-strl

3 output 0:

1 module schizo

1000

2 output 0:

% Surface

3

signal S in

4 loop

present S then

signal S in

emit 0

present S

10

end:

then

11

end;

emit 0

12

end;

% Depth

10

pause;

signal S' in

11

emit S;

15

pause;

12

end;

16

emit S';

13 end loop

17

end;

14 end module

18 end loop

Esterel

```

Duplicated loop body

"Surface copy" transfers control immediately to "depth copy"

[Tardieu & de Simone '04] (simplified)

```

1 module

2 schizo-cured2-strl

3 output 0:

1 module schizo

1000

2 output 0:

% Surface

3

signal S in

4 loop

Duplicated loop body

present S then

signal S in

emit 0

present S

10

"Surface copy" transfers control

end:

then

11

end;

immediately to "depth copy"

emit 0

12

end;

% Depth

10

Q: Complexity?

pause;

signal S' in

11

emit S;

15

pause;

12

end;

16

emit S';

13 end loop

17

end;

14 end module

18 end loop

Esterel

[Tardieu & de Simone

'04]

(simplified)

```

```

1 module

2 schizo-cured2-strl

3 output 0:

1 module schizo

1000

2 output 0:

% Surface

3

signal S in

4 loop

Duplicated loop body

present S then

signal S in

emit 0

present S

10

"Surface copy" transfers control

end:

then

11

end;

immediately to "depth copy"

emit 0

12

end;

% Depth

10

Q: Complexity?

pause;

signal S' in

11

emit S;

15

pause;

12

end:

A: Quadratic 😐

16

emit S';

13 end loop

end;

14 end module

18 end loop

Esterel

[Tardieu & de Simone

```

'04] (simplified)

```

1 module schizo

2 output 0;

3

4 100p

signal S in

present S

then

emit 0

end:

10

pause;

11

emit S:

12

end;

13 end loop

14 end module

```

#### Esterel

```

1 module schizo-cured

2 output bool 0;

3

while (true) {

bool S. Term:

1 module schizo

2 output 0:

Surf init

3

S = false:

4 loop

Term = false:

signal S in

10

fork

present S

11

0 = S;

then

pause;

emit 0

13

S = S || true;

end:

14

Term = true:

10

pause;

par

11

emit S:

16

do

12

end;

17

pause;

13 end loop

18

// Depth init

14 end module

19

S = false;

20

} while (! Term);

Esterel

21

join;

22

23 1

```

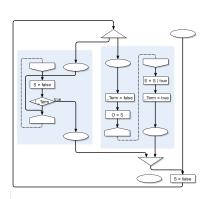

- "Surface initialization" at beginning of scope

- Delayed, concurrent "depth initialization"

```

1 module schizo-cured

2 output bool 0;

3

while (true) {

bool S. Term:

1 module schizo

2 output 0:

Surf init

3

S = false:

4 loop

Term = false:

signal S in

10

fork

present S

11

0 = S;

then

pause;

emit 0

13

S = S || true;

end:

14

Term = true:

10

pause;

par

11

emit S:

16

do

12

end;

17

pause;

13 end loop

18

// Depth init

14 end module

19

S = false;

20

} while (! Term);

Esterel

21

join;

22

23 1

```

- "Surface initialization" at beginning of scope

- Delayed, concurrent "depth initialization"

- Q: Complexity?

```

1 module schizo-cured

2 output bool 0;

3

while (true) {

bool S. Term:

1 module schizo

2 output 0:

3

S = false:

4 loop

Term = false:

signal S in

10

fork

present S

11

0 = S;

then

pause;

emit 0

13

S = S || true;

end:

14

Term = true:

10

pause;

par

11

emit S:

16

do

12

end;

17

pause;

13 end loop

18

// Depth init

14 end module

19

S = false;

20

} while (! Term);

Esterel

21

join;

22

23 1

```

- "Surface initialization" at beginning of scope

- Delayed, concurrent "depth initialization"

- Q: Complexity?

- A: Linear ©

```

1 module schizo-cured

2 output bool 0;

3

while (true) {

bool S. Term:

1 module schizo

2 output 0:

3

S = false:

4 100p

Term = false:

signal S in

10

fork

present S

11

0 = S:

then

12

pause;

emit 0

13

S = S || true;

end:

14

Term = true:

10

pause:

par

11

emit S:

16

do

12

end:

17

pause;

13 end loop

18

// Depth init

14 end module

19

S = false;

20

} while (! Term);

Esterel

21

join;

22

23 1

```

- "Surface initialization" at beginning of scope

- Delayed, concurrent "depth initialization"

- Q: Complexity?

- A: Linear ©

- Caveat: We only talk about signal reincarnation, i. e., instantaneously exiting and entering a signal scope

- Reincarnated **statements** still require duplication (quadratic worst case?)

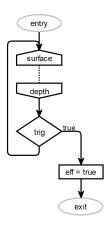

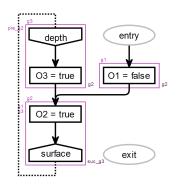

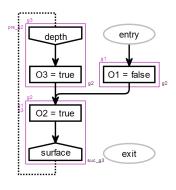

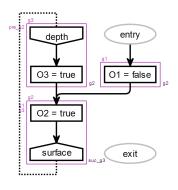

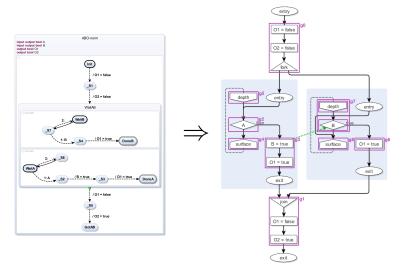

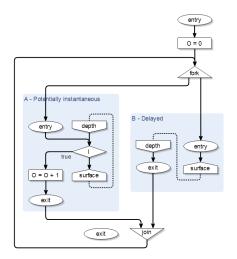

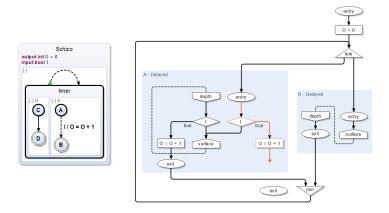

#### SCG for schizo-cured

```

1 module schizo-cured

2 output bool 0;

3 {

while (true) {

bool S. Term:

S = false:

Term = false:

10

fork

11

0 = S;

12

pause;

13

S = S || true;

14

Term = true:

15

par

16

do {

17

pause;

18

// Depth init

19

S = false;

20

} while (! Term);

21

join;

22

23 }

```

#### SCG for schizo-cured

```

1 module schizo-cured

2 output bool 0;

3

while (true) {

bool S. Term:

S = false:

Term = false:

10

fork

11

0 = S;

12

pause;

13

S = S || true;

14

Term = true:

15

par

16

do {

17

pause;

18

// Depth init

19

S = false;

20

} while (! Term);

21

join;

22

23

```

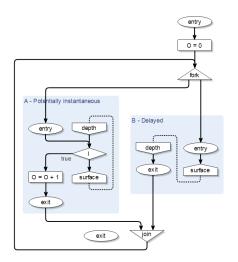

- Cycle now broken by delay

- Only the "depth initialization" of S creates a concurrent "initialize before update" scheduling dependence

- ► The join guard *g<sub>join</sub>* corresponds to the K0 output of the Esterel circuit synthesis

- ► Since g<sub>join</sub> depends on g<sub>fork</sub>, the reincarnation of parallel leads to non-constructive circuits, just as with Esterel circuit synthesis

- ► The join guard *g<sub>join</sub>* corresponds to the K0 output of the Esterel circuit synthesis

- Since g<sub>join</sub> depends on g<sub>fork</sub>, the reincarnation of parallel leads to non-constructive circuits, just as with Esterel circuit synthesis

- We may apply same solution: divide join into surface join g<sub>s-join</sub> and depth join g<sub>d-join</sub>

- ► The logic for suface join and depth is the same, except that in depth join, we replace g<sub>fork</sub> by false

- ► The join guard *g<sub>join</sub>* corresponds to the K0 output of the Esterel circuit synthesis

- Since g<sub>join</sub> depends on g<sub>fork</sub>, the reincarnation of parallel leads to non-constructive circuits, just as with Esterel circuit synthesis

- We may apply same solution: divide join into surface join g<sub>s-join</sub> and depth join g<sub>d-join</sub>

- ► The logic for suface join and depth is the same, except that in depth join, we replace g<sub>fork</sub> by false

- One can construct examples where both g<sub>s-join</sub> and g<sub>d-join</sub> are needed.

- ▶ If parallel is not instantaneous, only need  $g_{d-join}$ .

- $\triangleright$  The join guard  $g_{ioin}$  corresponds to the K0 output of the Esterel circuit synthesis

- $\triangleright$  Since  $g_{join}$  depends on  $g_{fork}$ , the reincarnation of parallel leads to non-constructive circuits, just as with Esterel circuit synthesis

- We may apply same solution: divide join into surface join  $g_{s-join}$ and depth join gd-ioin

- ▶ The logic for suface join and depth is the same, except that in depth join, we replace  $g_{fork}$  by false

- ▶ One can construct examples where both  $g_{s-join}$  and  $g_{d-join}$  are needed.

- If parallel is not instantaneous, only need  $g_{d-ioin}$ .

- ▶ In SCG, if thread terminates instantaneously in non-instantaneous parallel, we end in "unjoined exit" (visualized with small solid disk)

#### Statement Reincarnation

Consider I absent in initial tick, present in next tick

#### Statement Reincarnation

- Consider I absent in initial tick, present in next tick

- Must then increment O twice

#### Statement Reincarnation

- ► To remove cycle, must duplicate the part of the surface of the thread that might instantaneously terminate, i.e., nodes on instantaneous path from entry to exit

- ▶ The second increment of O leads to unjoined exit

1. Sequential Constructiveness **natural** for synchrony

- 1. Sequential Constructiveness **natural** for synchrony

- 2. Same semantic foundation from Extended SCCharts down to machine instructions/physical gates

- Modeler/programmer has direct access to target platform

- ▶ No conceptual breaks, e.g., when mapping signals to variables

- 1. Sequential Constructiveness **natural** for synchrony

- 2. Same semantic foundation from Extended SCCharts down to machine instructions/physical gates

- Modeler/programmer has direct access to target platform

- ▶ No conceptual breaks, e.g., when mapping signals to variables

- 3. Efficient synthesis paths for hw and sw, building on established techniques (circuit semantics, guarded actions, SSA, ...)

- 1. Sequential Constructiveness **natural** for synchrony

- 2. Same semantic foundation from Extended SCCharts down to machine instructions/physical gates

- ► Modeler/programmer has direct access to target platform

- ▶ No conceptual breaks, e.g., when mapping signals to variables

- 3. Efficient synthesis paths for hw and sw, building on established techniques (circuit semantics, guarded actions, SSA, ...)

- Treating advanced constructs as syntactic sugar simplifies down-stream synthesis (CISC vs. RISC)

- 1. Sequential Constructiveness **natural** for synchrony

- 2. Same semantic foundation from Extended SCCharts down to machine instructions/physical gates

- Modeler/programmer has direct access to target platform

- ▶ No conceptual breaks, e. g., when mapping signals to variables

- 3. Efficient synthesis paths for hw and sw, building on established techniques (circuit semantics, guarded actions, SSA, ...)

- Treating advanced constructs as syntactic sugar simplifies down-stream synthesis (CISC vs. RISC)

- Plenty of future work: compilation of Esterel-like languages, trade-off RISC vs. CISC, WCRT analysis, timing-predictable design flows (→ PRETSY), multi-clock, visualization, . . .

#### To Go Further

▶ J. Aguado, M. Mendler, R. von Hanxleden, I. Fuhrmann. Grounding Synchronous Deterministic Concurrency in Sequential Programming. In Proceedings of the 23rd European Symposium on Programming (ESOP'14), Grenoble, France, April 2014. http://rtsys.informatik.uni-kiel.de/~biblio/

http://rtsys.informatik.uni-kiel.de/~biblio/downloads/papers/esop14.pdf

R. von Hanxleden, M. Mendler, J. Aguado, B. Duderstadt, I. Fuhrmann, C. Motika, S. Mercer, O. O'Brien, and P. Roop. Sequentially Constructive Concurrency – A Conservative Extension of the Synchronous Model of Computation. ACM Transactions on Embedded Computing Systems, Special Issue on Applications of Concurrency to System Design, July 2014, 13(4s). http://rtsys.informatik.uni-kiel.de/~biblio/downloads/papers/tecs14.pdf