Alexander Schulz-Rosengarten Reinhard von Hanxleden, Michael Mendler

## Why restricting sequential constructiveness?

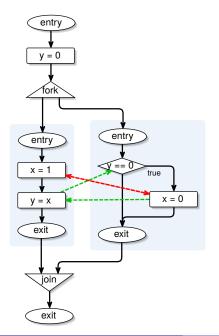

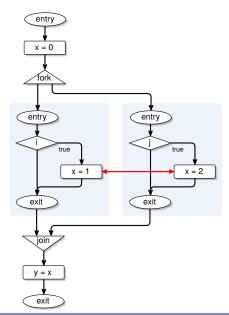

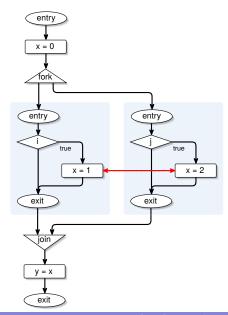

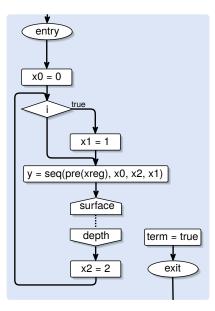

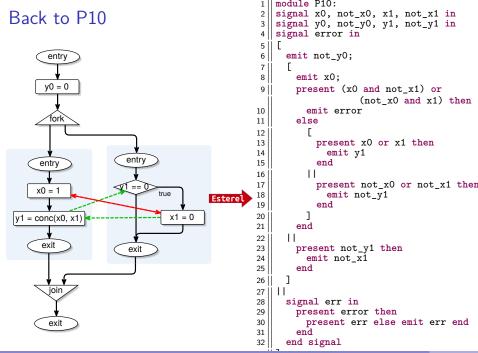

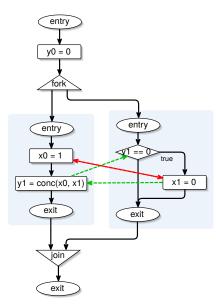

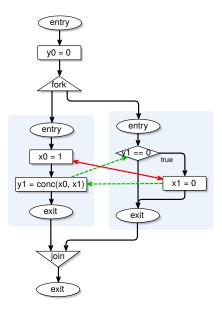

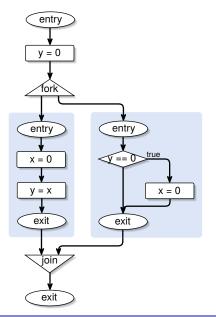

# Motivation: Program P10

| 1  | module P10           |      |

|----|----------------------|------|

| 2  | <pre>int x, y;</pre> |      |

| 3  | {                    |      |

| 4  | y = 0;               | //S1 |

| 5  | fork                 |      |

| 6  | x = 1;               | //S2 |

| 7  | y = x                | //S3 |

| 8  | par                  |      |

| 9  | if y == 0 then       | //S4 |

| 10 | x = 0                | //S5 |

| 11 | end                  |      |

| 12 | join                 |      |

| 13 | }                    |      |

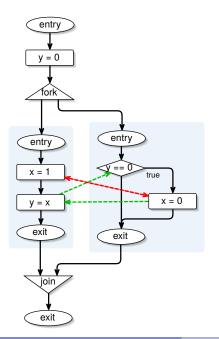

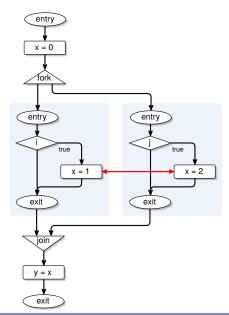

# Motivation: Program P10

| 1  | module P10           |      |

|----|----------------------|------|

| 2  | <pre>int x, y;</pre> |      |

| 3  | {                    |      |

| 4  | y = 0;               | //S1 |

| 5  | fork                 |      |

| 6  | x = 1;               | //S2 |

| 7  | y = x                | //S3 |

| 8  | par                  |      |

| 9  | if y == 0 then       | //S4 |

| 10 | x = 0                | //S5 |

| 11 | end                  |      |

| 12 | join                 |      |

| 13 | }                    |      |

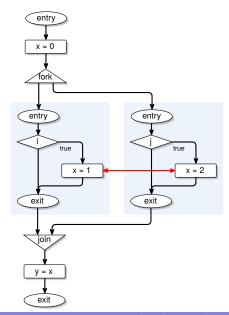

# Motivation: Program P10

| 1  | module P10           |      |

|----|----------------------|------|

| 2  | <pre>int x, y;</pre> |      |

| 3  | {                    |      |

| 4  | y = 0;               | //S1 |

| 5  | fork                 |      |

| 6  | x = 1;               | //S2 |

| 7  | y = x                | //S3 |

| 8  | par                  |      |

| 9  | if y == 0 then       | //S4 |

| 10 | x = 0                | //S5 |

| 11 | end                  |      |

| 12 | join                 |      |

| 13 | }                    |      |

|    |                      |      |

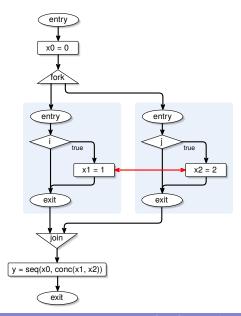

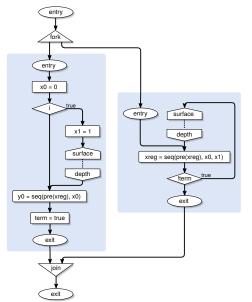

SC-admissible Schedule S1 — S2 — S3 — S4

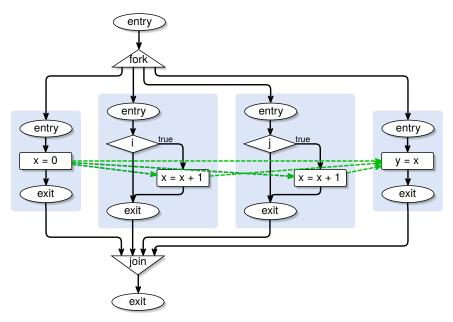

## P10

• is reactive (∃ SC-admissible Run)

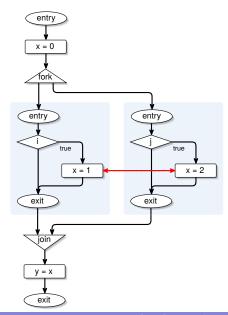

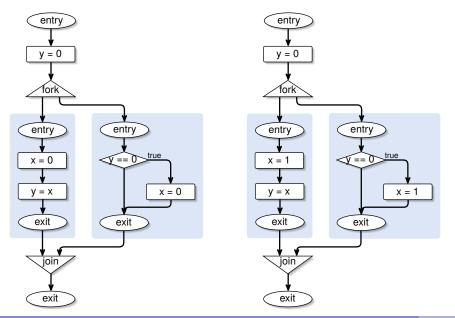

### P10

- is reactive ( $\exists$  SC-admissible Run)

- is determinate ( $\forall$  SC-admissible Runs : same determinate macro responses)

## P10

- is reactive ( $\exists$  SC-admissible Run)

- is determinate ( $\forall$  SC-admissible Runs : same determinate macro responses)

- is Sequentially Constructive

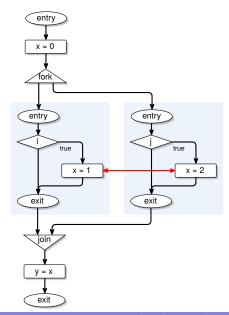

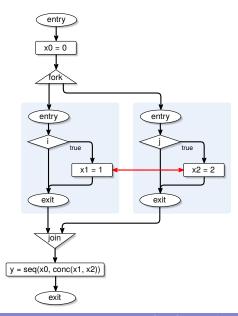

### P10

- is reactive (∃ SC-admissible Run)

- is determinate (∀ SC-admissible Runs : same determinate macro responses)

- is Sequentially Constructive

- but is executed in a speculative manner

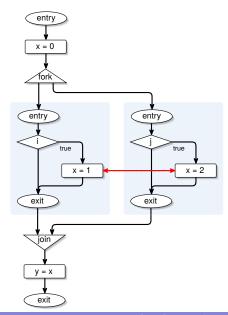

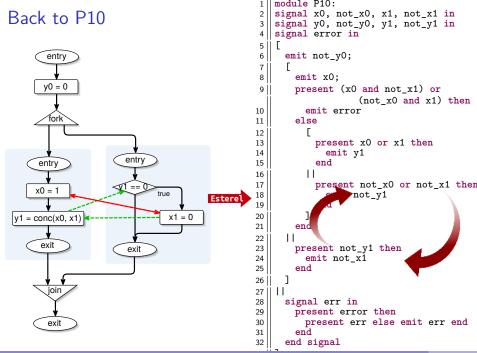

# YOU SHALL NOT

# **SPECULATE!**

P10:

- is reactive (∃ SC-admissible Run)

- is determinate (∀ SC-admissible Runs : same determinate macro responses)

- is Sequentially Constructive

- but is executed in a speculative manner

P10:

- is reactive (∃ SC-admissible Run)

- is determinate (∀ SC-admissible Runs : same determinate macro responses)

- is Sequentially Constructive

- but is executed in a speculative manner

Problem

The SC MoC allows speculation

P10:

- is reactive (∃ SC-admissible Run)

- is determinate (∀ SC-admissible Runs : same determinate macro responses)

- is Sequentially Constructive

- but is executed in a speculative manner

#### Problem

The SC MoC allows speculation  $\Rightarrow$  SC programs may form non-constructive (delay sensitive) circuits

## Strict Sequential Constructiveness is Sequential Constructiveness without speculation

## Strict Sequential Constructiveness is Sequential Constructiveness without speculation

#### How can we eliminate speculation?

Idea

Ground SC in constructiveness in the spirit of Esterel

### Idea

Ground SC in constructiveness in the spirit of Esterel

Constructive Esterel:

has no speculation

#### Idea

Ground SC in constructiveness in the spirit of Esterel

Constructive Esterel:

- has no speculation

- always transforms into delay-insensitive (constructive) circuits

#### Idea

Ground SC in constructiveness in the spirit of Esterel

Constructive Esterel:

- has no speculation

- always transforms into delay-insensitive (constructive) circuits

#### Idea

Ground SC in constructiveness in the spirit of Esterel

Constructive Esterel:

- has no speculation

- always transforms into delay-insensitive (constructive) circuits

but

• requires globally consistent signal states

#### Idea

Ground SC in constructiveness in the spirit of Esterel

#### Constructive Esterel:

- has no speculation

- always transforms into delay-insensitive (constructive) circuits

but

- requires globally consistent signal states

- has no shared variables (write & read)

- Transformation into SSA form

- sequential variable behavior

- sequential variable behavior

- iur protocol

- Transformation into SSA form

- sequential variable behavior

- iur protocol

- 2 Translation into Esterel

- sequential variable behavior

- iur protocol

- 2 Translation into Esterel

- signal encoding

- sequential variable behavior

- iur protocol

- 2 Translation into Esterel

- signal encoding

- SSA functions encoding

- sequential variable behavior

- iur protocol

- 2 Translation into Esterel

- signal encoding

- SSA functions encoding

- Sterel constructiveness check

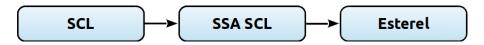

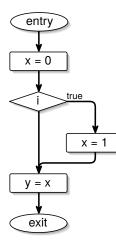

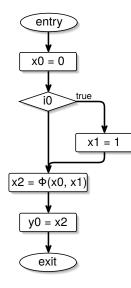

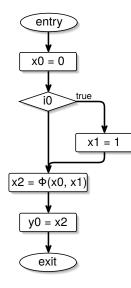

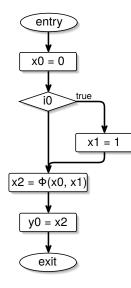

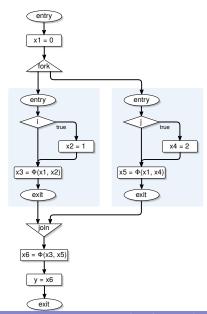

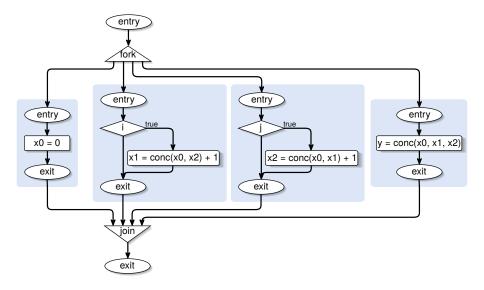

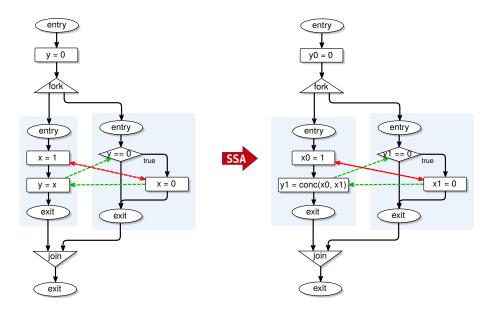

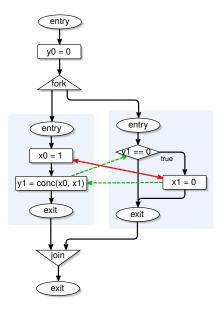

## Procedure

Split up variables into versions

## Procedure

- Split up variables into versions

- Introduce *\phi*-functions to merge variable versions

• Each variable is assigned only once (statically)

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Minimal placement of  $\phi$ -nodes using a dominator analysis

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Minimal placement of  $\phi$ -nodes using a dominator analysis

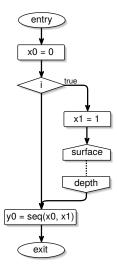

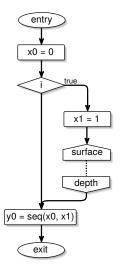

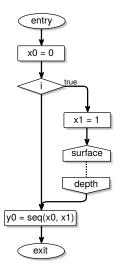

# Static Single Assignment Form

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Minimal placement of  $\phi$ -nodes using a dominator analysis

- Intermediate representation based on a CFG

# Static Single Assignment Form

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Minimal placement of  $\phi$ -nodes using a dominator analysis

- Intermediate representation based on a CFG

# Static Single Assignment Form

- Each variable is assigned only once (statically)

- Only one reaching definition for each read (def-use-chains)

- Minimal placement of  $\phi$ -nodes using a dominator analysis

- Intermediate representation based on a CFG

What about SCGs with concurrency?

#### Problem

$\phi$ -functions cannot handle concurrency

| i     | j     | У |

|-------|-------|---|

| false | false |   |

| false | true  |   |

| true  | false |   |

| true  | true  |   |

| i     | j     | У |

|-------|-------|---|

| false | false | 0 |

| false | true  |   |

| true  | false |   |

| true  | true  |   |

| i     | j     | У |

|-------|-------|---|

| false | false | 0 |

| false | true  | 2 |

| true  | false |   |

| true  | true  |   |

| i     | j     | У |

|-------|-------|---|

| false | false | 0 |

| false | true  | 2 |

| true  | false | 1 |

| true  | true  |   |

| i     | j     | У      |

|-------|-------|--------|

| false | false | 0      |

| false | true  | 2      |

| true  | false | 1      |

| true  | true  | reject |

SC-specific merge functions:

• Sequential override

SC-specific merge functions:

- Sequential override

- Encode concurrency

SC-specific merge functions:

- Sequential override

- Encode concurrency

- Detect confluent writes

SC-specific merge functions:

- Sequential override

- Encode concurrency

- Detect confluent writes

- Reject conflicting writes

SC-specific merge functions:

- Sequential override

- Encode concurrency

- Detect confluent writes

- Reject conflicting writes

# Variable Representation: $\langle x^p, x \rangle$ Inspired by valued signals. $x^p$ : Presence signal x: Actual variable value

SC-specific merge functions:

- Sequential override

- Encode concurrency

- Detect confluent writes

- Reject conflicting writes

#### Variable Representation: $\langle \mathbf{x}^p, \mathbf{x} \rangle$

Inspired by valued signals.

- $\mathbf{x}^p$ : Presence signal

- x: Actual variable value

#### SC-specific merge functions:

- Sequential override

- Encode concurrency

- Detect confluent writes

- Reject conflicting writes

# Variable Representation: $\langle x^p, x \rangle$ Inspired by valued signals.

- x<sup>p</sup>: Presence signal

- x: Actual variable value

```

||\operatorname{conc}(\langle \mathbf{x}_{i}^{p}, \mathbf{x}_{i} \rangle, \langle \mathbf{x}_{j}^{p}, \mathbf{x}_{j} \rangle) :=

present \mathbf{x}_i^p then

2

3

present x_i^p then

if x_i == x_j then

4

return \langle \mathbf{x}_i^p, \mathbf{x}_i \rangle

5

else

6

reject

7

else

8

return \langle \mathbf{x}_i^p, \mathbf{x}_i \rangle

9

else

10

present \mathbf{x}_{i}^{p} then

11

return \langle \mathbf{x}_{i}^{p}, \mathbf{x}_{j} \rangle

12

else

13

return \langle absent, nil \rangle

14

```

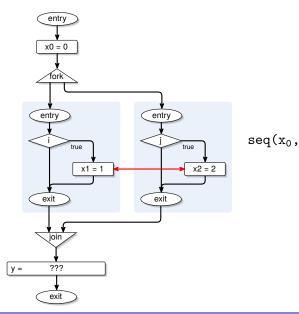

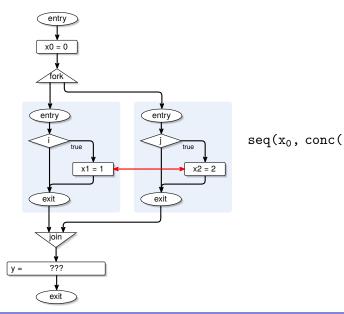

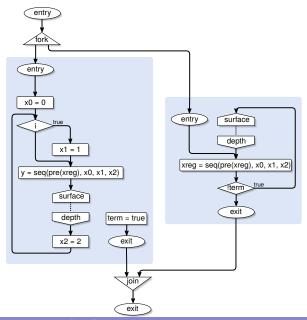

$seq(x_0, conc(x_1,$

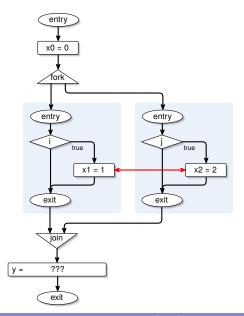

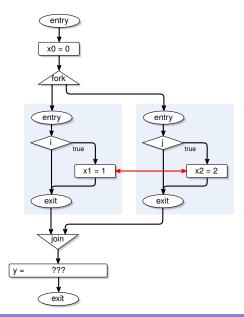

$seq(x_0, conc(x_1, x_2))$

$seq(x_0, conc(x_1, x_2))$

| i     | j     | У      |

|-------|-------|--------|

| false | false | 0      |

| false | true  | 2      |

| true  | false | 1      |

| true  | true  | reject |

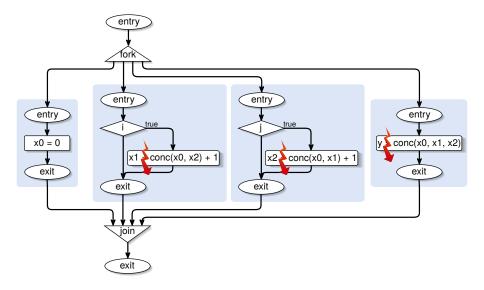

Delays

- Delays

- Merge functions use a variable with signals and implicit reset

Delays

Merge functions use a variable with signals and implicit reset

Loops

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Updates

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Updates

- iur protocol ordering

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Updates

- iur protocol ordering

- Confluent by definition

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Updates

- iur protocol ordering

- Confluent by definition

- Interface

- Delays

- Merge functions use a variable with signals and implicit reset

- Loops

- Merge expressions require explicit sequential ordering

- Updates

- iur protocol ordering

- Confluent by definition

- Interface

- SSA renaming

### SSA Form: Delays

| 1      | $ \operatorname{conc}(\langle \mathbf{x}_{i}^{p},\mathbf{x}_{i}\rangle,\langle \mathbf{x}_{j}^{p},\mathbf{x}_{j}\rangle)$ := |

|--------|------------------------------------------------------------------------------------------------------------------------------|

| 2<br>3 | present $\mathbf{x}_i^p$ then                                                                                                |

| 3      | present $\mathbf{x}_j^p$ then                                                                                                |

| 4      | if $x_i = x_j$ then                                                                                                          |

| 4<br>5 | $\texttt{return} \hspace{0.1 in} \langle {\tt x}_{i}^{p}, {\tt x}_{i} \rangle$                                               |

| 6      | else                                                                                                                         |

| 7      | reject                                                                                                                       |

| 8      | else                                                                                                                         |

| 9      | $\texttt{return} \hspace{0.1 in} \langle \mathtt{x}_{i}^{p}, \mathtt{x}_{i} \rangle$                                         |

| 10     | else                                                                                                                         |

| 11     | present $\mathbf{x}_j^p$ then                                                                                                |

| 12     | return $\langle \mathtt{x}_{j}^{p}, \mathtt{x}_{j}  angle$                                                                   |

| 13     | else                                                                                                                         |

| 14     | $ $ return $\langle absent, nil \rangle$                                                                                     |

|        |                                                                                                                              |

• Presence signals are reset to absent

- Presence signals are reset to absent

- Runtime concurrent conflicts can be detected

- Presence signals are reset to absent

- Runtime concurrent conflicts can be detected

- Merge function cannot resolve value without write in the same tick

Solution:

• Resolve and save variable values in each tick

- Resolve and save variable values in each tick

- Store values in register variables

- Resolve and save variable values in each tick

- Store values in register variables

- Use *pre* to consider values of the previous tick in merge expressions

- Resolve and save variable values in each tick

- Store values in register variables

- Use *pre* to consider values of the previous tick in merge expressions

- Reduce merge expression based on tick borders

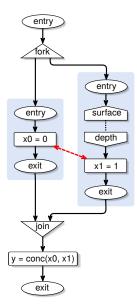

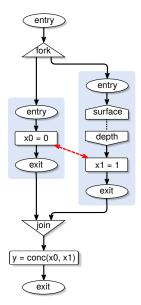

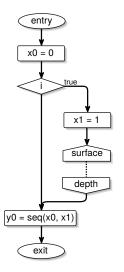

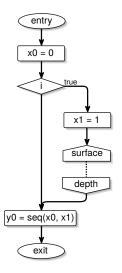

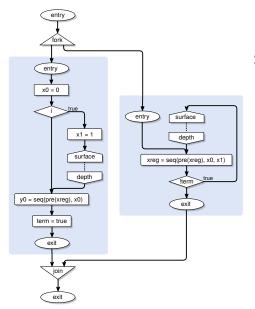

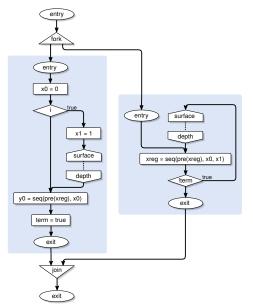

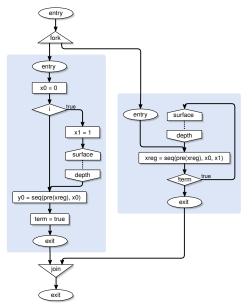

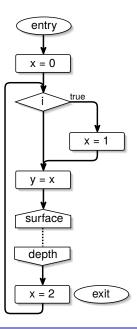

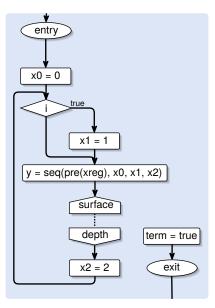

#### SSA Form: Loops

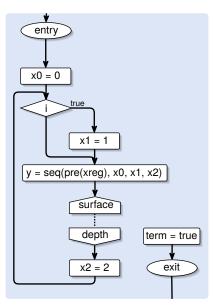

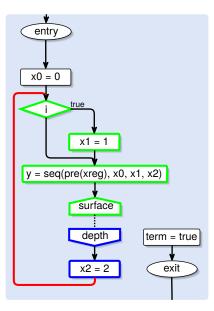

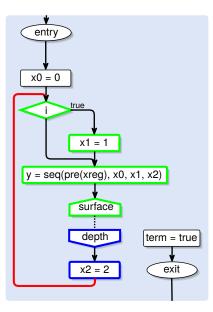

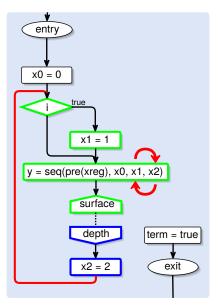

# SSA Form: Loops

• Merge expressions require static ordering

- Merge expressions require static ordering

- Wrong ordering due to simple structure analysis

- Merge expressions require static ordering

- Wrong ordering due to simple structure analysis

Solution:

• Surface-Depth analysis

- Merge expressions require static ordering

- Wrong ordering due to simple structure analysis

- Surface-Depth analysis

- Requires a pause that is always executed

- Merge expressions require static ordering

- Wrong ordering due to simple structure analysis

- Surface-Depth analysis

- Requires a pause that is always executed

- Switch order of writes in the surface with depth

- Merge expressions require static ordering

- Wrong ordering due to simple structure analysis

- Surface-Depth analysis

- Requires a pause that is always executed

- Switch order of writes in the surface with depth

# SSA Form: Updates

### SSA Form: Updates

## SSA Form: Updates

x = x + 1

$x = x + 1 \rightarrow xup = 1$

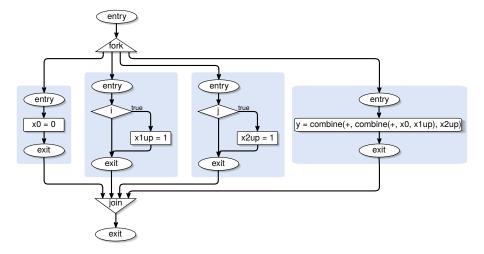

$x = x + 1 \rightarrow xup = 1$   $\downarrow$ combine(+,  $x_{init}$ , xup)

$$x = x + 1 \rightarrow xup = 1$$

$\downarrow$

combine(+,  $x_{init}$ ,  $xup$ )

```

||| \operatorname{combine}(f, \langle \mathbf{x}^p, \mathbf{x} \rangle, \langle \mathbf{x}^p_{up}, \mathbf{x}_{up} \rangle) :=

present x^p then

2

present x_{up}^p then

3

return \langle \mathbf{x}^p, f(\mathbf{x}, \mathbf{x}_{up}) \rangle

4

else

5

return \langle \mathbf{x}^p, \mathbf{x} \rangle

6

else

7

present x_{up}^p then

8

reject

9

else

10

return \langle absent, nil \rangle

11

```

$x = x + 1 \rightarrow xup = 1$   $\downarrow$ combine(+,  $x_{init}$ , xup)

```

||| \operatorname{combine}(f, \langle \mathbf{x}^p, \mathbf{x} \rangle, \langle \mathbf{x}^p_{up}, \mathbf{x}_{up} \rangle) :=

present x^p then

2

3

present x_{up}^p then

return \langle \mathbf{x}^p, f(\mathbf{x}, \mathbf{x}_{up}) \rangle

4

else

5

return \langle x^p, x \rangle

6

else

7

present x_{up}^p then

8

reject

9

else

10

return \langle absent, nil \rangle

11

```

#### • Special seq function for updates

$x = x + 1 \rightarrow xup = 1$   $\downarrow$ combine(+,  $x_{init}$ , xup)

- Special seq function for updates

- Requires partial static schedule to generate merge expressions

#### SSA Form: Updates Solved

```

module IO

1

input int I;

2

output int 0;

3

4

{

if I < 0 then

5

I = 0

6

end;

7

0 = I;

8

9

pause;

0 = 0 * I

10

11 || }

```

```

module IO

1

input int I;

2

output int 0;

3

{

4

if I < 0 then

5

I = 0

6

end;

7

0 = I;

8

pause;

9

0 = 0 * I

10

11 || }

```

• SSA renaming should not violate the original interface

```

module IO

1

input int I;

2

output int O;

3

{

4

if I < 0 then

5

I = 0

6

end;

7

0 = I;

8

pause;

9

0 = 0 * I

10

11 || }

```

- SSA renaming should not violate the original interface

- Inputs must be read from the environment in each tick

```

module IO

1

input int I;

2

output int O;

3

{

4

if I < 0 then

5

I = 0

6

end;

7

0 = I;

8

pause;

9

0 = 0 * I

10

11

```

- SSA renaming should not violate the original interface

- Inputs must be read from the environment in each tick

- Inputs can be locally overridden

```

module IO

1

input int I;

2

3

output int O;

{

4

if I < 0 then

5

T = 0

6

end;

7

0 = I;

8

pause;

9

0 = 0 * I

10

11

```

- SSA renaming should not violate the original interface

- Inputs must be read from the environment in each tick

- Inputs can be locally overridden

- Outputs must be conveyed to the environment in each tick

# SSA Form: Interface Solved

```

1 module IO-SSA

2 input int I;

int IO;

3

output int O;

4

int 00, 01, 0reg;

5

bool term = false;

6

ſ

7

fork

8

if I < 0 then

9

IO = O

10

end;

11

00 = seq(I, I0)

12

13

pause;

01 = pre(0reg) * I;

14

term = true

15

```

```

par

PauseLoop:

Oreg = seq(pre(Oreg), 00, 01);

O = Oreg;

if !term then

pause;

goto PauseLoop

end

join

}

```

16

17

18

19

20

21

22

23

24

25

Translation of

• program structure

Translation of

- program structure

- variables

Translation of

- program structure

- variables

Esterel data-types:

Variables

Translation of

- program structure

- variables

- Variables

- Valued signals

Translation of

- program structure

- variables

- Variables

- Valued signals

- Pure signals

Translation of

- program structure

- variables

- Variables

- Valued signals

- Pure signals

| Presence Encoding                       |               |                |  |

|-----------------------------------------|---------------|----------------|--|

| $\mathtt{x}_i^p \setminus \mathtt{x}_i$ | present       | absent         |  |

| present<br>absent                       | true<br>undef | false<br>undef |  |

Translation of

- program structure

- variables

- Variables

- Valued signals

- Pure signals

| Presence Encoding                       |         |        |  |

|-----------------------------------------|---------|--------|--|

| $\mathtt{x}_i^p \setminus \mathtt{x}_i$ | present | absent |  |

| present                                 | true    | false  |  |

| absent                                  | undef   | undef  |  |

| Dual-Rail Encoding       |                  |               |  |  |

|--------------------------|------------------|---------------|--|--|

| $x_i \setminus not\_x_i$ | present          | absent        |  |  |

| present<br>absent        | illegal<br>false | true<br>undef |  |  |

$\mathbf{x}_i$  = true  $\rightarrow$  emit  $\mathbf{x}_i$

$egin{array}{cccc} {f x}_i &= {f true} & \longrightarrow & {f emit} & {f x}_i \ {f x}_i &= {f false} & \longrightarrow & {f emit} & {f not}_{\_}{f x}_i \end{array}$

```

x_i = true

emit x<sub>i</sub>

\rightarrow

x_i = false

emit not_x<sub>i</sub>

\rightarrow

present errorExpr(e) then

emit error

else

Γ

present trueExpr(e) then

emit x<sub>i</sub>

end

\mathbf{x}_i = e

\rightarrow

11

present falseExpr(e) then

emit not_x<sub>i</sub>

end

٦

end

```

```

if (e) then

//then-block

else

//else-block

end

```

```

present errorExpr(e) then

emit error

else

Γ

present trueExpr(e) then

% then-block

end

11

present falseExpr(e) then

% else-block

end

٦

end

```

$\rightarrow$

$x_i$ :

trueExpr:  $x_i$

falseExpr: not\_x<sub>i</sub>

```

\begin{array}{l} \mathbf{x}_i:\\ \mathsf{trueExpr:} \ \mathbf{x}_i\\ \mathsf{falseExpr:} \ \mathsf{not}\_\mathbf{x}_i\\ \textit{conc}(e_i,e_j):\\ \mathsf{errorExpr:} \ (\mathsf{trueExpr}(e_i) \land \mathsf{falseExpr}(e_j)) \lor\\ (\mathsf{falseExpr}(e_i) \land \mathsf{trueExpr}(e_j))\\ \mathsf{trueExpr:} \ \mathsf{trueExpr}(e_i) \lor \mathsf{trueExpr}(e_j)\\ \mathsf{falseExpr:} \ \mathsf{falseExpr}(e_i) \lor \mathsf{falseExpr}(e_j)\\ \end{array}

```

```

\mathbf{x}_i:

trueExpr: \mathbf{x}_i

falseExpr: not x<sub>i</sub>

conc(e_i, e_j):

errorExpr: (trueExpr(e_i) \land falseExpr(e_i)) \lor

(falseExpr(e_i) \land trueExpr(e_i))

trueExpr: trueExpr(e_i) \lor trueExpr(e_i)

falseExpr: falseExpr(e_i) \lor falseExpr(e_i)

seq(e_i, e_j):

trueExpr: trueExpr(e_i) \lor (\neg \mathsf{falseExpr}(e_i) \land \mathsf{trueExpr}(e_i))

falseExpr: falseExpr(e_i) \lor (\neg trueExpr(e_i) \land falseExpr(e_i))

```

# Not constructive in Esterel $\Rightarrow$ not Strict SC

## Confluent P10 Variants

#### Confluent P10 Variants

## Confluent P10 Variants

```

1||

1||||

emit not_y0;

emit not_y0;

3

3

emit not_x0;

emit x0;

4

4 |

5

present (x0 and not_x1) or (

5

present (x0 and not_x1) or (

not x0 and x1) then

not x0 and x1) then

emit error

emit error

6

6

7

else

7

else

8

8

present x0 or x1 then

present x0 or x1 then

9

9

emit v1

emit y1

10

10

end

end

11

11

12

12

13

present not_x0 or not_x1 then

present not_x0 or not_x1 then

13

emit not_y1

emit not_y1

14

14

end

15

15

end

16

16

end

end

17

17

11

18

18

19

present not_y1 then

19

present not_y1 then

emit x1

20

emit not x1

20

21

end

21

end

22

22

23 || | |

23

24

signal err in

signal err in

24

25

present error then

25

present error then

26

present err else emit err end

26

present err else emit err end

27

end

27

end

28

end signal

28

end signal

```

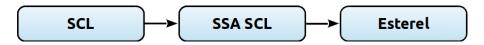

### New Compile Chain

• Optimized translation for SCEst

- Optimized translation for SCEst

- Code optimization based on SSA

- Optimized translation for SCEst

- Code optimization based on SSA

- Loop unrolling for (bounded) instantaneous loops

- Optimized translation for SCEst

- Code optimization based on SSA

- Loop unrolling for (bounded) instantaneous loops

- Dynamic scheduling of updates

- Optimized translation for SCEst

- Code optimization based on SSA

- Loop unrolling for (bounded) instantaneous loops

- Dynamic scheduling of updates

- Reduction merge expression insertion