## Synchronous Languages—Lecture 07

#### Prof. Dr. Reinhard von Hanxleden

Christian-Albrechts Universität Kiel Department of Computer Science Real-Time Systems and Embedded Systems Group

7 May 2020 Last compiled: May 5, 2020, 11:56 hrs

Esterel V—The Constructive Circuit Semantics

1. What is the derivative (Ableitung) of a program?

- 1. What is the derivative (Ableitung) of a program?

- 2. How is the program transition of an Esterel program defined?

- 1. What is the derivative (Ableitung) of a program?

- 2. How is the program transition of an Esterel program defined?

- 3. How do program transitions express logical coherence?

- 1. What is the derivative (Ableitung) of a program?

- 2. How is the program transition of an Esterel program defined?

- 3. How do program transitions express logical coherence?

- 4. Which semantics for Esterel exist?

- 1. What is the derivative (Ableitung) of a program?

- 2. How is the program transition of an Esterel program defined?

- 3. How do program transitions express logical coherence?

- 4. Which semantics for Esterel exist?

- 5. What are the *constructive coherence laws*, how do they differ from the logical coherence law?

#### Overview

#### The Circuit Semantics

Constructive circuits The basic circuit translation Translating the Esterel kernel

# Translating Esterel to Circuits

- Can consider Esterel programs as SW or HW descriptions

- As it turns out, the HW-equivalent of constructiveness is that the synthesized circuit is delay-independent

- This gives a firm, physical base for the constructive semantics we just considered

# Translating Esterel to Circuits

- Can consider Esterel programs as SW or HW descriptions

- As it turns out, the HW-equivalent of constructiveness is that the synthesized circuit is delay-independent

- This gives a firm, physical base for the constructive semantics we just considered

- Can in turn simulate this synthesized HW-circuit in SW

- This is just what the Esterel v5 compiler does

- Can then also take advantage of HW optimization techniques

- Use BDD-based techniques to check constructiveness

```

module P1:

input I;

output 0;

signal S1, S2 in

present I then emit S1 end

||

present S1 else emit S2 end

||

present S2 then emit 0 end

end signal

end module

```

```

module P1:

input I;

output 0;

signal S1, S2 in

present I then emit S1 end

||

present S1 else emit S2 end

||

present S2 then emit 0 end

end signal

end module

```

```

circuit C1:

S1 = I

S2 = \neg S1

O = S2

```

$\equiv$

```

module P1:

input I;

output 0;

signal S1, S2 in

present I then emit S1 end

||

present S1 else emit S2 end

||

present S2 then emit 0 end

end signal

end module

```

```

circuit C1:

S1 = I

S2 = \neg S1

O = S2

```

$\equiv$

Resulting circuit is acyclic

```

module P1:

input I;

output 0;

signal S1, S2 in

present I then emit S1 end

||

present S1 else emit S2 end

||

present S2 then emit 0 end

end signal

end module

```

```

circuit C1:

S1 = I

S2 = \neg S1

O = S2

```

$\equiv$

- Resulting circuit is acyclic

- Hence always stabilizes

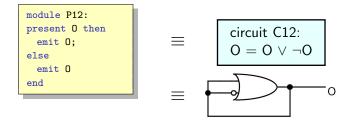

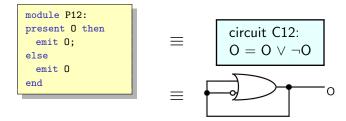

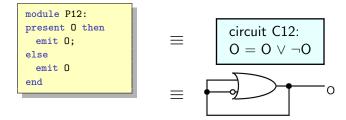

- Reactive and deterministic

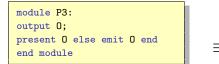

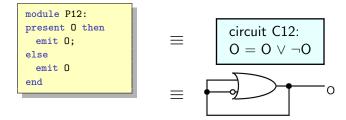

module P3:

output 0;

present O else emit O end end module

#### $\equiv$

module P3: output 0; present 0 else emit 0 end

end module

≡

circuit C3:  $O = \neg O$

circuit C3:

$$0 = \neg 0$$

Not reactive

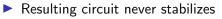

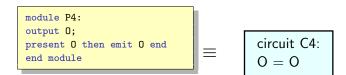

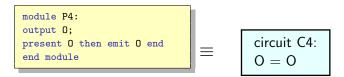

module P4:

output O;

present O then emit O end end module

$\equiv$

- Resulting circuit can stabilize at different values

- Not deterministic

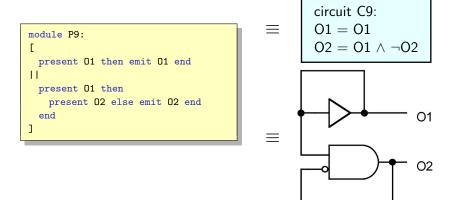

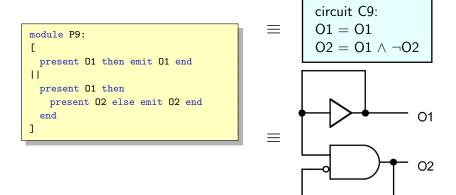

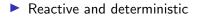

```

module P9:

[

present 01 then emit 01 end

||

present 01 then

present 02 else emit 02 end

end

]

```

```

module P9:

[

present 01 then emit 01 end

]

present 01 then

present 02 else emit 02 end

end

]

```

```

circuit C9:

01 = 01

02 = 01 \land \neg 02

```

$\equiv$

But not constructive!

Reactive and deterministic

- Reactive and deterministic

- Meaning: If it stabilizes, there is only one possible value for each wire's voltage

- Reactive and deterministic

- Meaning: If it stabilizes, there is only one possible value for each wire's voltage

- But: Does it always stabilize?

Consider following delay assignment:

Consider following delay assignment:

Circuit is reactive and deterministic (Newtonian model)

Consider following delay assignment:

Circuit is reactive and deterministic (Newtonian model)

But: Circuit never stabilizes (Vibration model)

Consider following delay assignment:

- Circuit is reactive and deterministic (Newtonian model)

- But: Circuit never stabilizes (Vibration model)

- Hence: Electrical stabilization is not the conjunction of reactivity and determinism!

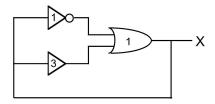

```

module P13:

present I then

present 02 then emit 01 end

else

present 01 then emit 02 end

end

```

=

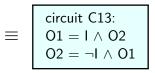

$$\equiv \begin{array}{|c|c|} circuit C13: \\ 01 = I \land 02 \\ 02 = \neg I \land 01 \end{array}$$

$$\equiv \begin{array}{|c|c|} circuit C13: \\ O1 = I \land O2 \\ O2 = \neg I \land O1 \end{array}$$

Reactive and deterministic

#### Circuit Semantics—Introduction

$$\equiv \begin{array}{|c|c|} circuit C13: \\ O1 = I \land O2 \\ O2 = \neg I \land O1 \end{array}$$

- Reactive and deterministic

- Cyclic, yet always stabilizes

#### Circuit Semantics—Introduction

$$\equiv \begin{array}{c} \text{circuit C13:} \\ \text{O1} = \text{I} \land \text{O2} \\ \text{O2} = \neg \text{I} \land \text{O1} \end{array}$$

- Reactive and deterministic

- Cyclic, yet always stabilizes

- Hence: Electrical stabilization does not require acyclicity

#### Circuit Semantics—Introduction

- Reactive and deterministic

- Cyclic, yet always stabilizes

- Hence: Electrical stabilization does not require acyclicity

- In fact: Electrical stabilization equivalent to constructiveness

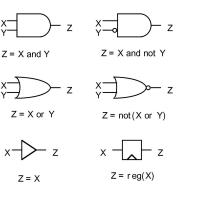

Basic building blocks

- Allow insertion of arbitrary delays

- Registers:

$$\blacktriangleright reg(X) = 0 \rightarrow pre(X)$$

Constructive Boolean (intuitionistic) logic:

Evaluate equations with constant folding rules

- Evaluate equations with constant folding rules

- ▶ not  $0 \rightarrow 1$

- ▶ not  $1 \rightarrow 0$

- Evaluate equations with constant folding rules

- ▶ not 0 → 1

- ▶ not  $1 \rightarrow 0$

- ▶ 1 or  $x \rightarrow 1$

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- ▶ 0 or  $0 \rightarrow 0$

- Evaluate equations with constant folding rules

- not  $0 \rightarrow 1$

- not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- ▶ 0 or  $0 \rightarrow 0$

- $\blacktriangleright \ 0 \ \text{and} \ x \to 0$

- $\blacktriangleright$  x and 0  $\rightarrow$  0

- ▶ 1 and  $1 \rightarrow 1$

- Evaluate equations with constant folding rules

- not  $0 \rightarrow 1$

- not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- ▶ 0 or  $0 \rightarrow 0$

- ▶ 0 and  $x \rightarrow 0$

- $\blacktriangleright$  x and 0  $\rightarrow$  0

- ▶ 1 and  $1 \rightarrow 1$

- There is no law of excluded middle (x or not  $x \rightarrow 1$ )!

- Evaluate equations with constant folding rules

- ▶ not  $0 \rightarrow 1$

- ▶ not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- $\blacktriangleright \ 0 \text{ or } 0 \to 0$

- $\blacktriangleright \ 0 \ \text{and} \ x \to 0$

- $\blacktriangleright$  x and 0  $\rightarrow$  0

- ▶ 1 and  $1 \rightarrow 1$

- There is no law of excluded middle (x or not  $x \rightarrow 1$ )!

- Circuit equations yield solution iff circuit is delay insensitive (i.e., the original Esterel program is constructive)

- Evaluate equations with constant folding rules

- ▶ not  $0 \rightarrow 1$

- ▶ not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- $\blacktriangleright \ 0 \text{ or } 0 \to 0$

- $\blacktriangleright \ 0 \ \text{and} \ x \to 0$

- $\blacktriangleright$  x and 0  $\rightarrow$  0

- $\blacktriangleright \ 1 \text{ and } 1 \rightarrow 1$

- There is no law of excluded middle (x or not  $x \rightarrow 1$ )!

- Circuit equations yield solution iff circuit is delay insensitive (i.e., the original Esterel program is constructive)

- Propagation of 1's corresponds to

- Evaluate equations with constant folding rules

- ▶ not  $0 \rightarrow 1$

- ▶ not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- $\blacktriangleright \ 0 \text{ or } 0 \to 0$

- $\blacktriangleright \ 0 \ \text{and} \ x \to 0$

- x and  $0 \rightarrow 0$

- $\blacktriangleright \ 1 \text{ and } 1 \to 1$

- There is no law of excluded middle (x or not  $x \rightarrow 1$ )!

- Circuit equations yield solution iff circuit is delay insensitive (i.e., the original Esterel program is constructive)

- Propagation of 1's corresponds to Must-analysis

- Evaluate equations with constant folding rules

- ▶ not  $0 \rightarrow 1$

- ▶ not  $1 \rightarrow 0$

- ▶ 1 or x → 1

- $\blacktriangleright$  x or  $1 \rightarrow 1$

- $\blacktriangleright \ 0 \text{ or } 0 \to 0$

- $\blacktriangleright \ 0 \ \text{and} \ x \to 0$

- x and  $0 \rightarrow 0$

- $\blacktriangleright \ 1 \text{ and } 1 \to 1$

- There is no law of excluded middle (x or not  $x \rightarrow 1$ )!

- Circuit equations yield solution iff circuit is delay insensitive (i.e., the original Esterel program is constructive)

- Propagation of 1's corresponds to Must-analysis

- Propagation of 0s corresponds to Cannot-analysis

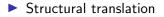

- Structural translation

- Follows state semantics

- Associate registers with "1" statements (pause)

- Associate combinational logic with all other statements

- Structural translation

- Follows state semantics

- Associate registers with "1" statements (pause)

- Associate combinational logic with all other statements

- Build up program-circuit from subcircuits

- Structural translation

- Follows state semantics

- Associate registers with "1" statements (pause)

- Associate combinational logic with all other statements

- Build up program-circuit from subcircuits

- Additional boot register to implement initial state

- Structural translation

- Follows state semantics

- Associate registers with "1" statements (pause)

- Associate combinational logic with all other statements

- Build up program-circuit from subcircuits

- Additional boot register to implement initial state

- Basic circuit translation does not address schizophrenia (see later)

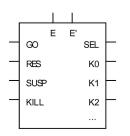

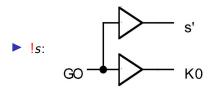

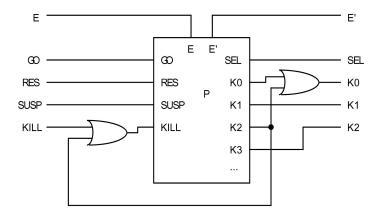

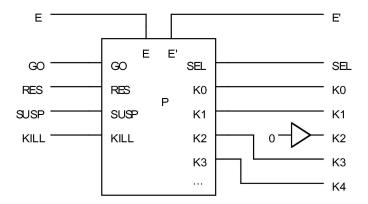

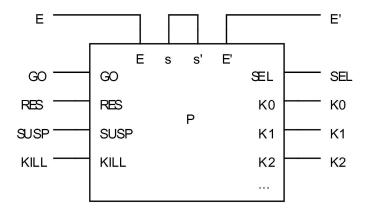

#### Interface for subcircuits

Inputs:

- ► GO: Starts statement afresh

- RES: Resumes execution of a selected statement

- SUSP: Suspend execution of the statement

- Registers keep their current value unless killed because of the KILL input

- KILL: Unsets statement's registers in case of a trap exit

#### Interface for subcircuits contd.

CAU

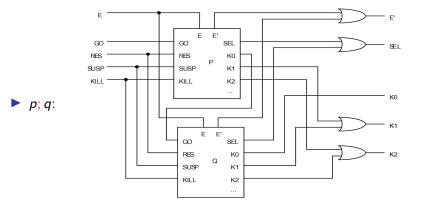

#### Outputs:

- SEL: Indicates that a state in statement is currently selected for resumption, i.e. that some internal pause register is set

- Is simply the disjunction of the internal registers.

- K0, K1, ...: Completion codes (1-hot encoding)

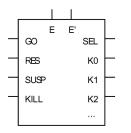

#### Interface for subcircuits contd.

- **E** and **E**': input/output signal interface

- Are compound pins or buses

- Contain one elementary pin per signal visible in the scope of the current statement.

- May freely extract specific signals s or s' out of E or E'.

- As for the K pins, the E' pins are explicitly unset when the statement is not executed

- ▶ I.e. when  $\neg$ (GO  $\lor$  (RES  $\land$  SEL))

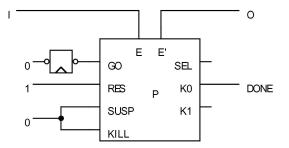

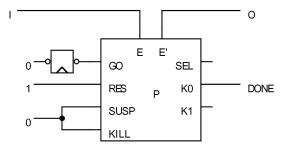

## The Global Environment

#### The Global Environment

- Boot register sets GO input in initial instant

- At each clock cycle

- set RES

- clock the registers

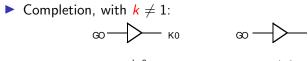

K2

K2

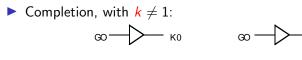

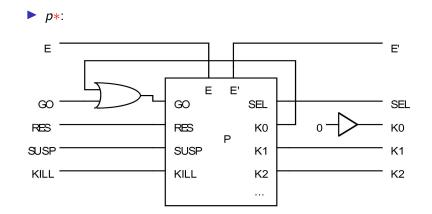

$\blacktriangleright k = 1$  (pause):

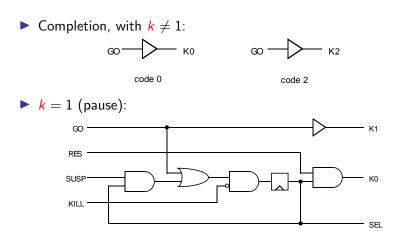

► *s*?*p*,*q*:

► *s* ⊃ *p*:

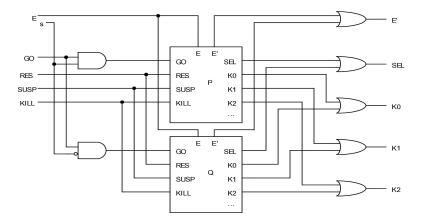

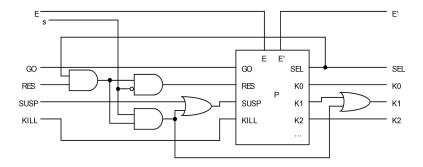

# Translating the Esterel Kernel p || q:

▶ p || q:

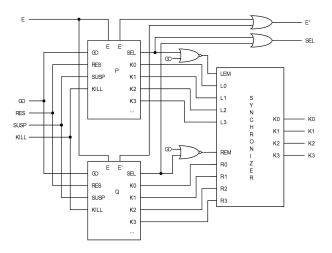

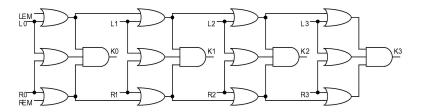

#### ▶ *p* || *q* (contd):

- The synchronizer computes the maximum of the completion codes

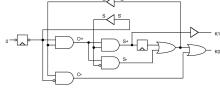

- Implemented with this (constructive) circuit:

► {*p*}:

► ↑*p*:

► *p\s*:

#### Example

module P2: signal S in emit S; present 0 then present S then pause end present; emit 0 end present end signal

#### Example

circuit C2:

$$B = \neg REG(1) // Boot$$

$$S = B$$

$$R = REG(B \land O \land S) // pause$$

$$O = (B \land O \land \neg S) \lor R$$

$$K0 = (B \land \neg O) \lor (B \land O \land \neg S) \lor R$$

$$K1 = B \land O \land S$$

#### Example

circuit C2:

$$B = \neg \operatorname{REG}(1) // \operatorname{Boot}$$

$$S = B$$

$$R = \operatorname{REG}(B \land O \land S) // \operatorname{pause}$$

$$O = (B \land O \land \neg S) \lor R$$

$$K0 = (B \land \neg O) \lor (B \land O \land \neg S) \lor R$$

$$K1 = B \land O \land S$$

## To Go Further

- Gérard Berry, The Constructive Semantics of Pure Esterel, Draft book, current version 3.0, Dec. 2002, Chapters 10 and 11,

- http://www-sop.inria.fr/members/Gerard.Berry/ Papers/EsterelConstructiveBook.zip